CPLD útskýrt: Leiðbeiningar um forritanleg rökfræði tæki

Í kraftmiklum heimi rafrænnar hönnunar eru flókin forritanleg rökfræðibúnað (CPLDS) áberandi sem fjölhæf verkfæri, blandast óaðfinnanlega aðlögunarhæfni, nákvæmni og skilvirkni.Þessi tæki gjörbyltu hringrásarhönnun með því að kynna forritanlegar þjóðhagsfrumur og ríkjandi samtengingar fylki, sem gerir kleift að búa til flóknar rökfræðiaðgerðir með ótrúlegri áreiðanleika.Frá upphafi þeirra á níunda áratugnum til lykilhlutverks síns í nútíma atvinnugreinum eins og neti, bifreiðum og geimferða, hafa CPLDs reynst nauðsynleg fyrir þig að leita bæði sveigjanleika og afkasta.Þessi grein grefur inn í ferð CPLDS, sérkenni þeirra, hagnýt forrit og forritunaraðferðir sem gera þá að hornsteini í stafrænni rökfræði.Vörulisti

Yfirlit yfir CPLD

Innan yfirráða flókinna forritanlegra rökfræðibúnaðar (CPLDS) uppgötvar maður háþróaðan teppi forritanlegra rökrétta frumna, samofin í gegnum ríkjandi samtengingu fylki.Þessar þjóðhagsfrumur (MC) og inntak/úttak (I/O) einingalínur gera þér kleift að hanna rafrásir fimur og stilla mannvirkin fyrir einstaka aðgerðir.Ólíkt tækjum sem eru ráðalaus af flóknum tímasetningu samtengis, nota CPLDS óhreyfanlegar málmvír.Þetta einkenni veitir þeim stöðuga og fyrirsjáanlega klukkuhegðun, sem gerir tímasetningarspár áreiðanlegri og nákvæmari.

Ferðin og nýtingin

Á áttunda áratugnum boðaði tilkomu forritanlegra rökfræðibúnaðar (PLDS) og hlúði að því að fara í átt að forritanlegum þjóðhagseiningum.Þessi breyting kynnti nægan sveigjanleika í hönnun og aðgreindi þá frá kyrrstæðum stafrænum hringrásum, þó að notagildi þeirra hafi upphaflega verið bundið við einfaldari hringrásir.Tilkoma CPLDS um miðjan níunda áratuginn gjörbylti þessu landslagi og braut brautina fyrir flókna hringrásarhönnun.Síðan þá hafa þeir ofið sig í efni atvinnugreina eins og netkerfis, rafeindatækni í bifreiðum, CNC vinnslu og geimferðakerfum.Þú getur rifjað upp um það hvernig CPLDS einfalda ferla sem einu sinni kröfðust nákvæmrar handavinnu og merktu ótrúlegt stökk í skilvirkni.

Sérkenni CPLDS

CPLDS aðgreina sig með aðlögunarhæfri forritun sinni, umfangsmikilli samþættingu, snögga þróunargetu og víðtækri notagildi ásamt hagkvæmum framleiðslukostnaði.Þeir höfða til þeirra sem eru með lágmarks vélbúnaðarreynslu og þjóna sem áreiðanlegar og öruggar vörur sem þurfa ekki tæmandi prófanir.Sem vitnisburður um hreysti þeirra í stórum stíl hringrásarhönnun gegna CPLDs lykilhlutverki í þróun frumgerðar og þjóna keyrðum undir 10.000 einingum og fela í sér gagnlega hæfni fyrir þig.Augnarleikinn sem CPLDs aðlagast að þróa kröfur verkefnisins fær þeim oft þakklæti og leggja áherslu á raunverulegan fjölhæfni þeirra í kraftmiklu umhverfi.

Umsóknaraðferðir

Þessar samþættu hringrásir gera þér kleift að útfæra rökfræðiaðgerðir sem eru sniðnar að þörfum þeirra með því að nota bæði skýringarmyndir og vélbúnaðarlýsingu á þróunarpöllum.Til dæmis, við hönnun svara vél, skýringarmynda og vélbúnaðarlýsingar eru útbúnar og teknar saman á tölvu.Með því að nota niðurhalssnúru er kóðinn fluttur til CPLD fyrir forritun í kerfinu, sem samanstendur af prófunum, bilanaleit og efla hönnun.Með góðum árangri er smíðað hönnun síðan fjöldaframleidd með því að endurtaka CPLD flís.Í verkefnum eins og umferðarljósakerfum verður endurtekning á hönnunarferlinu nauðsynleg, svipað og að endurbyggja hús til að endurheimta nýmæli þess.Þessi endurtekna aðferðafræði leggur oft grunninn til að ná tökum, efla bæði færni og sjálfstraust.

Leiðandi afbrigði

Í gegnum árin hafa fyrirtæki eins og Altera, grindurnar og Xilinx afhjúpað áberandi línur af CPLDS.Athyglisverð dæmi eru Altera's EPM7128S, Grindurnar LC4128V, og Xilinx XC95108 .Þessar gerðir hafa fundið áberandi hlutverk í fjölbreyttum alþjóðlegum forritum.Þeir sem hafa haft forréttindi að vinna með þessar aðgreindu vörur gera oft athugasemdir við fíngerða en öflugan mun sem hámarka tiltekna virkni.Þetta endurspeglar fínt valferli sem hefur áhrif á sérstakar kröfur um verkefnið, þar sem hvert afbrigði hefur sitt einstaka áfrýjun.

Auðkenning og flokkun FPGA og CPLD

|

Þátt |

CPLD |

FPGA |

|

Rökrétt hegðunarmyndun |

Myndaðu rökrétt hegðun með því að nota uppbyggingu vöru.

Dæmi: Lattice Isplsi Series, Xilinx XC9500 Series, Altera Max7000s

Series, Lattice Mach Series |

Myndaðu rökrétt hegðun með því að nota töflu leitaraðferð.

Dæmi: Xilinx Spartan Series, Altera Flex10K, ACEX1K Series |

|

Hæfi |

Hentar fyrir reiknirit og samsetningar rökfræði, virkar

Betri með takmarkaða kallar og ríkar vöruskilmála |

Hentar fyrir röð rökfræði, virkar betur með

mannvirki sem eru rík af kveikjum |

|

Tímasetning |

Stöðug raflögn uppbygging veitir samræmda og

fyrirsjáanlegar tímasetningar tafir |

Segluðu raflögn uppbygging leiðir til ófyrirsjáanlegrar tímasetningar

Tafir |

|

Forritun sveigjanleika |

Fastum innri hringrásum er breytt fyrir forritun.

Forritun á rökfræði blokkarstigs er notuð |

Innri raflögn er breytt fyrir forritun.Rökfræði

Forritun hliðarstigs gerir kleift að auka sveigjanleika |

|

Samþætting |

Lægri samþætting miðað við FPGA |

Hærri samþætting með flóknari raflögn og

Framkvæmd rökfræði |

|

Auðvelda notkun |

Auðveldara í notkun með forritun með E2PROM eða Fastflash.

Enginn ytri minni flís er krafist |

Krefst ytri minni til að geyma forritun

upplýsingar, sem leiða til flóknari notkunar |

|

Hraði og fyrirsjáanleiki |

Hraðari hraða og betri tímasetningu fyrirsjáanleika vegna

Snúður samtenging milli rökfræðiblokka |

Hægari hraði og minna fyrirsjáanleg tímasetning vegna

GATE-stig forritun og dreift samtenging |

|

Forritunartækni |

Notar E2PROM eða flass minni forritun.Forritunargögn

er haldið þegar kerfið er sent.Styður forritun á a

forritari eða í kerfinu |

Byggt á SRAM forritun.Forritunargögn glatast þegar

Kerfið er slökkt og verður að endurhlaða.Styður kraftmikið

Stillingar |

|

Trúnað |

Býður upp á betri trúnað |

Veitir lægri trúnað |

|

Orkunotkun |

Almennt meiri orkunotkun, sérstaklega með

Hærri samþætting |

Lægri orkunotkun miðað við CPLD |

Forritunarmál CPLD

Að greina hversu flókin forritanleg rökfræði tæki (CPLDS) eru forrituð er hornsteinn í að föndra fjölhæfar vélbúnaðarlausnir.Sögulegar aðferðir við forritun CPLDs hafa reitt sig á stigamyndir eða vélbúnaðarlýsingu tungumál (HDL), þar sem Verilog HDL og VHDL eru aðal val.Valið tungumál getur mótað bæði hönnunarstefnu og rekstrar skilvirkni útfærslna.

• Verilog HDL: Verilog HDL er þykja vænt um einfalda setningafræði og öfluga uppgerð getu, sem endurspeglar aðferðafræði sem notuð er við stafræna rökfræði.Samþætting þess við ELECTION Design Automation (EDA) verkfæri gerir þér kleift að gera óaðfinnanlega myndun og uppgerð.Sýnt hefur verið fram á að C-eins og setningafræði Verilog lækkar aðgangshindrunina fyrir þá sem eru með forritunargrundvöll og flýta ferðinni frá hönnun til dreifingar yfir fjölbreytt úrval iðnaðargreina.

• VHDL: VHDL býður upp á vandaðri og svipmikinn valkost fyrir HDL forritun.Það er oft valið fyrir verkefni sem krefjast nákvæmra skjala og strangra tékka, einkenni að verðmæti í geimferðum og varnarmálum.Þú getur tekið fram að þrátt fyrir hugsanlegt flækjustig VHDL í smærri verkefnum styður öguð uppbygging þess að búa til einstaklega áreiðanlegar hönnun, nauðsyn í umhverfi þar sem öryggi er ráðandi.

Um okkur

ALLELCO LIMITED

Lestu meira

Fljótur fyrirspurn

Vinsamlegast sendu fyrirspurn, við munum svara strax.

NMOS smárar: hönnun, notkun og forrit

á 2024/12/29

The Fast Fourier Transform (FFT): Byltingar á stafrænni merkisvinnslu

á 2024/12/29

Vinsæl innlegg

-

Flóknar tölvuuppsetningar tölvur: hvernig þær breyttu tölvunarfræði?

á 8000/04/18 147770

-

USB-C pinout og eiginleikar

á 2000/04/18 112006

-

Notkun Xilinx Unified Simulation Primitives: Alhliða leiðbeiningar um FPGA hönnun og uppgerð

á 1600/04/18 111351

-

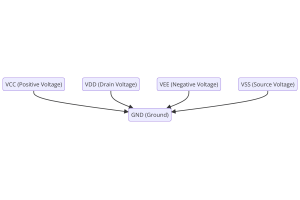

Aflgjafaspenna í rafeindatækni: Merking VCC, VDD, VEE, VSS og GND

á 0400/04/18 83768

-

RJ45 tengihandbók: Pinout, raflögn, snúrutegundir og notar

á 1970/01/1 79564

-

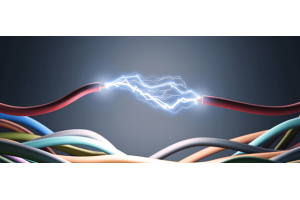

Endanleg leiðarvísir um vír litakóða í nútíma rafkerfum

Hvernig rafkerfin okkar nota liti er ekki bara fyrir útlit.Hver vírlitur gefur nú til kynna ákveðna aðgerð, sem gerir það auðveldara að bera kennsl á og meðhöndla rafmagn íhluta rétt við uppsetning...á 1970/01/1 66959

-

Hreinsunarhandbók: Virkni, einkenni, prófanir og skipti fyrir ákjósanlegan afköst vélarinnar

Hreinsunarventillinn er lykilatriði í kerfi bíls sem hjálpar til við að halda loftinu hreinu með því að stjórna eldsneytisgufum áður en þeir geta sloppið út í andrúmsloftið.Þetta hjálpar ekki aðein...á 1970/01/1 63098

-

Gæði (q) þáttur: jöfnur og forrit

Gæðaþátturinn, eða 'Q', er mikilvægur þegar athugað er hversu vel inductors og resonators vinna í rafrænu kerfum sem nota útvarpsbylgjur (RF).'Q' mælir hversu vel hringrás lágmarkar orkutap og hefu...á 1970/01/1 63040

-

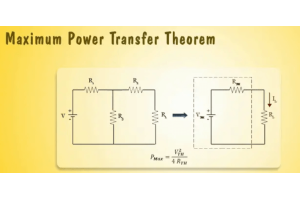

Að ná hámarksafköstum með hámarks valdaflutnings setningu

Setning hámarks aflflutnings útskýrir hvernig orka frá uppruna, svo sem rafhlöðu eða rafall, rennur til tengds álags.Það sýnir nákvæmlega ástand þar sem álagið fær mestan kraft.Þessi grein fjallar ...á 1970/01/1 54096

-

A23 rafhlöðuforskriftir og eindrægni

A23 rafhlaðan er lítil, strokkalaga rafhlaða með háspennu.Einnig kallað 23A, 23AE eða MN21, það keyrir á 12 volt og miklu hærri en AA eða AAA rafhlöður.Sérstök hönnun þess gerir það fullko...á 1970/01/1 52184