EP1C4F400C8 FPGA: Aðgerðir, forskriftir, forritun og valkostur

Ef þú ert að vinna með forritanlega rökfræði gefur EP1C4F400C8 þér hagnýtt jafnvægi á frammistöðu og kostnaði.Í þessari grein lærir þú hvað þessi FPGA er, lykilatriði þess eins og rökfræði getu, minni og I/O valkostir og hvernig uppbygging þess styður áreiðanlega hönnun.Þú munt einnig sjá forskriftir þess, forrit í kerfum, forritunarferli og hvernig það er borið saman við svipaða hluta.Vörulisti

Hvað er EP1C4F400C8?

The EP1C4F400C8 er meðlimur í Cyclone FPGA fjölskyldu Intel (áður Altera), hannaður sem hagkvæm og áreiðanleg forritanleg rökfræði lausn.Þetta tæki er byggt á 0,13 µM SRAM ferli og býður upp á miðlungs rökfræðiþéttleika og sveigjanlega I/O valkosti innan samningur FBGA-400 pakka.Hringrásarfjölskyldan, sem inniheldur tæki eins og EP1C3, EP1C6, EP1C12 og EP1C20, var búin til til að koma jafnvægi á afköst og hagkvæmni fyrir stigstærð hönnun, sem gerir kleift að flæði milli þéttleika og pakka.Það er þekkt fyrir stöðugleika og víðtæka ættleiðingu og er enn traust val í arfleifð hönnun.

Ertu að leita að EP1C4F400C8?Hafðu samband við okkur til að athuga núverandi lager, leiðslutíma og verðlagningu.

EP1C4F400C8 CAD módel

EP1C4F400C8 tákn

EP1C4F400C8 fótspor

EP1C4F400C8 3D líkan

EP1C4F400C8 aðgerðir

• Rökfræði getu

EP1C4F400C8 býður upp á um 4.000 rökfræðiþætti, skipulögð í 400 rökfræðiblokkir (rannsóknarstofur).Þetta gerir það hentugt fyrir miðstigshönnun sem krefst hóflegs þéttleika rökfræði en viðhalda hagkvæmni.

• Innbyggt minni

Það samþættir um það bil 76,5 kbit af innbyggðu minni.Þessi innri RAM styður gagnabuffi, geymslu og litla minni aðgerðir og dregur úr þörfinni fyrir ytri minni íhluti í mörgum hönnun.

• High I/O Count

Tækið býður upp á 301 notendastillanlegan I/O pinna í 400 bolta FBGA pakkanum sínum.Þessi háa pinnaafjöldi gerir kleift að taka rík tengsl fyrir flókin kerfi sem krefjast margra útlægra viðmóta.

• Breiður I/O staðlar stuðningur

Það styður marga I/O staðla þar á meðal LVTTL, LVCMOS, SSTL-2, SSTL-3 og mismunadrif LVD.Þessi sveigjanleiki gerir FPGA kleift að tengja beint við margvíslegar nútíma rökfræði fjölskyldur og minni tæki.

• Háhraða mismunadrif

Með LVDs styðja allt að 640 Mbps, höndlar FPGA skjótar kröfur um gagnaflutning.Þetta gerir það hagnýtt fyrir forrit eins og háhraða samskiptatengla og hratt stafrænt viðmót.

• Klukkustjórnun með PLLS

Flísin samþættir tvær fasa læstar lykkjur (PLL) og átta Global Clock Networks.Þessir eiginleikar gera kleift að ná nákvæmri klukkuframleiðslu, margföldun og stýringu fyrir tímasetningu.

• Lítilspennu kjarnaaðgerð

Starfandi við nafnvirðan 1,5 V kjarnaspennu, jafnvægir afköst tækisins með minni orkunotkun.Þetta spennustig var fínstillt fyrir 0,13 µm CMOS tækni sem notuð var við framleiðslu hennar.

• Sveigjanleg I/O spennu

FPGA styður I/O spennu 1,5 V, 1,8 V, 2,5 V og 3,3 V yfir mismunandi banka.Þessi fjölhæfni gerir það kleift að tengja bæði við arfleifð og nútíma kerfisíhluti.

• SRAM-byggð stilling

Eins og aðrir Cyclone FPGA, þá er það SRAM-undirstaða og þarfnast endurstillingar við hverja uppsprettu.Þetta veitir sveigjanleika fyrir uppfærslur en þarf einnig utanaðkomandi stillingarbúnað eða stjórnandi.

• Bitstream þjöppunarstuðningur

EP1C4F400C8 styður þjappað bitream hleðslu við stillingar.Þetta dregur úr utanaðkomandi minniskröfum og flýtir fyrir stillingartímum.

• PCI samræmi

Það felur í sér innbyggðan stuðning við PCI staðla (33/66 MHz, 32/64-bita).Þessi aðgerð gerir kleift að samþætta tækið beint í kerfum sem krefjast PCI tengi án viðbótar brúa rökfræði.

Uppbygging Cyclone Lab

Skýringarmyndin sýnir uppbyggingu Logic Array (LAB) sem notuð er í Cyclone FPGA eins og EP1C4F400C8.Hver rannsóknarstofa tengist neti samtenginga: Row samtengingar, samtengingar á dálki og staðbundnum samtengingum, sem leiðarmerki milli rökfræðiþátta og annarra blokka.Bein tengsl samtengingar veita hratt, lágstýringarleiðir við aðliggjandi rannsóknarstofur, bæta tímasetningarárangur í merkisleiðum.Þessi arkitektúr er mikilvægur vegna þess að hann kemur jafnvægi á sveigjanleika með skilvirkni, sem gerir FPGA kleift að takast á við flókna hönnun en halda hraða og svæðum bjartsýni.

Cyclone I/O Banks skýringarmynd

Skýringarmyndin sýnir I/O banka uppbyggingu Cyclone FPGA eins og EP1C4F400C8.Tækinu er skipt í fjóra I/O banka, sem hver knúinn er af eigin framboðsstrætó, sem gerir kleift að blanda mismunandi spennustaðlum innan eins FPGA.Allir bankar styðja fjölbreytt úrval af I/O stöðlum þar á meðal LVTTL, LVCMOS, LVDS, RSDS og SSTL, en bankar 1 og 3 styðja einnig 3,3-V PCI fyrir eindrægni við arfakerfi.Þessi sveigjanlega I/O arkitektúr er mikilvægur vegna þess að hann gerir kleift að fá óaðfinnanlega samþættingu við fjölbreytt ytri tæki og tengi, sem gerir FPGA aðlagast ýmsum forritum.

EP1C4F400C8 forskriftir

|

Tegund |

Færibreytur |

|

Framleiðandi |

Altera/Intel |

|

Röð |

Cyclone® |

|

Umbúðir |

Bakki |

|

Staða hluta |

Úrelt |

|

Fjöldi rannsóknarstofna/CLB |

400 |

|

Fjöldi rökfræðiþátta/frumna |

4000 |

|

Heildar vinnsluminni |

78.336 |

|

Fjöldi i/o |

301 |

|

Spenna - framboð |

1.425V ~ 1.575V |

|

Festingartegund |

Yfirborðsfesting |

|

Rekstrarhiti |

0 ° C ~ 85 ° C (TJ) |

|

Pakki / mál |

400-BGA |

|

Pakki birgjabúnaðar |

400-fbga (21 × 21) |

|

Grunnvörunúmer |

EP1C4 |

EP1C4F400C8 forrit

1. Stafræn merkisvinnsla (DSP)

Hægt er að forrita EP1C4F400C8 til að framkvæma verkefni eins og síun, FFT og merkis mótun.Samsetning þess af rökfræðiþáttum og innbyggðu minni gerir það hentugt fyrir háhraða vinnslu.Þetta gerir það kleift að skipta um hefðbundna DSP flís fyrir sveigjanlega FPGA lausn sem hægt er að forrita fyrir mismunandi reiknirit.

2.. Innbyggt og stjórnkerfi

Í iðnaðar- og innbyggðum kerfum er þessi FPGA oft notaður til að innleiða sérsniðna stýringar, raðtæki og ríkisvélar.Endurstillanleg rökfræði þess gerir kleift að sníða hegðun vélbúnaðar einmitt að kerfisþörfum.Með því að samþætta stjórnunarrökfræði í FPGA er fjöldi ytri íhluta fækkaður, bætir áreiðanleika og lækkandi kostnað.

3.. Samskipti og tengibrúa

Tækið styður marga I/O staðla og getur virkað sem brú milli mismunandi samskiptareglur.Það er oft notað til að tengja PCI, LVD, SDRAM og önnur tengi óaðfinnanlega innan kerfis.Þetta gerir það mjög gagnlegt í netbúnaði, innbyggðum stýringum og arfleifð-til-nútímalegum viðskiptum.

4.. Gagnaöflun og vinnsla

Með hátt I/O framboð og sveigjanlegt minni er EP1C4F400C8 vel hentugur fyrir gagnaöflunarkerfi.Það getur beint tengt ADC og skynjara, unnið úr gögnum í tíma og undirbúið þau fyrir geymslu eða sendingu.Slík forrit eru algeng í lækningatækjum, prófunarbúnaði og vísindalegum mælingum.

EP1C4F400C8 Svipaðir hlutar

|

Forskrift |

EP1C4F400C8 |

EP1C4F400C8N |

EP1C4F400C8NAA |

EP1C4F400C6N |

EP1C4F324C8N |

EP1C4T144C8N |

|

Framleiðandi |

Altera (Intel) |

Altera (Intel) |

Altera (Intel) |

Altera (Intel) |

Altera (Intel) |

Altera (Intel) |

|

FPGA fjölskylda |

Cyclone (EP1C4) |

Cyclone (EP1C4) |

Cyclone (EP1C4) |

Cyclone (EP1C4) |

Cyclone (EP1C4) |

Cyclone (EP1C4) |

|

Rökfræðiþættir (LES) |

4.000 |

4.000 |

4.000 |

4.000 |

4.000 |

4.000 |

|

Innbyggt minni (bitar) |

~ 76,5 kbits |

~ 76,5 kbits |

~ 76,5 kbits |

~ 76,5 kbits |

~ 76,5 kbits |

~ 76,5 kbits |

|

I/O pinnar |

301 |

301 |

301 |

301 |

249 |

97 |

|

Pakki / mál |

400-fbga |

400-fbga |

400-fbga |

400-fbga |

324-fbga |

144-TQFP |

|

Hraða bekk |

C8 |

C8 |

C8 |

C6 (hraðari) |

C8 |

C8 |

|

Grunnspenna |

1,5 V. |

1,5 V. |

1,5 V. |

1,5 V. |

1,5 V. |

1,5 V. |

|

Rekstrartímabil.Svið |

0 ° C ~ 85 ° C. |

0 ° C ~ 85 ° C. |

0 ° C ~ 85 ° C. |

0 ° C ~ 85 ° C. |

0 ° C ~ 85 ° C. |

0 ° C ~ 85 ° C.

|

EP1C4F400C8 forritunarskref

Áður en þú getur notað EP1C4F400C8 FPGA, verður þú að hlaða hönnun þína í tækið.Forritun felur í sér að stilla FPGA með bitastraumi skrá svo hún viti hvernig á að haga sér sem fyrirhugaða hringrás.

1. Veldu Stillingarkerfi og stilltu MSEL pinna

Þú byrjar á því að velja stillingarkerfið sem hentar best uppsetningunni þinni, svo sem virkt raðnúmer, óvirkan rað eða JTAG.Þetta er gert með því að stilla MSEL pinna á ákveðin rökfræði stig áður en það er gert.Hver stilling notar mismunandi pinna og samskiptareglur, svo þú þarft að staðfesta eindrægni við hönnunarverkfæri og stillingarminni.Að gera rétt val hér tryggir slétt stillingarferli.

2. Berðu afl og frumstilltu tækið

Næst skaltu knýja upp kjarna FPGA og I/O teina innan tilgreindra spennusviðs.Við ræsingu, hafðu NCONFIG pinnann lágt til að halda tækinu í endurstillingu þar til framboðsspennan er stöðug.Þegar þú ert stöðugur sleppir þú endurstillingu og tækið gefur til kynna reiðubúin með því að keyra NSTATUS pinnann.Þetta tryggir að FPGA er rétt frumstilla áður en stillingar hefjast.

3. Sendu stillingarnar bitastraumsins

Á þessu stigi sendir þú stillingargagnaskrána (BitStream) í FPGA með því að nota valið kerfið þitt.Í virkum rað- eða óbeinum raðstillingu kemur bitastraumurinn frá utanaðkomandi minnisbúnaði en JTAG leyfir bein forritun með snúru.Tækið les stöðugt í stillingargögnum þar til því er lokið.Hönnunarhugbúnaðurinn þinn býr til þennan bitastraum til að passa við rökfræði kröfur þínar.

4. Staðfestu árangursríka stillingu (conf_done)

Þegar FPGA lýkur hleðslu, fullyrðir það Conf_Done pinnann til að sýna að stillingargögn hafi verið móttekin.Á sama tíma framkvæmir tækið innri frumstillingu eins og hreinsunarskrár og virkjar I/O.Ef conf_done tekst ekki að fara hátt þýðir það venjulega að stillingargögnin eða uppsetningin hefur villu.Að horfa á þennan pinna er einfaldasta leiðin til að sannreyna að ferlinu sé lokið.

5. Framkvæmdu valfrjálst endurstillingu kerfisins

Að lokum hefurðu möguleika á að uppfæra eða endurforrita FPGA án þess að fjarlægja það af borðinu.Með því að nota JTAG eða innbyggðan stjórnandi geturðu hlaðið nýjum bitastraumi beint, sem er gagnlegt fyrir uppfærslur á vélbúnaði.Þessi sveigjanleiki gerir þér kleift að breyta, kemba eða uppfæra kerfið þitt jafnvel eftir dreifingu.Það tryggir að FPGA-byggð hönnun þín geti aðlagast með tímanum að breyttum kröfum.

EP1C4F400C8 Kostir og gallar

Kostir

• Hagkvæm val fyrir miðstigshönnun

• Hátt I/O fjöldi miðað við svipuð þéttleika tæki

• Sveigjanleg spenna og I/O venjulegur stuðningur

• Stuðlað af þroskuðum verkfærum og skjölum

• Lægri raforkunotkun en eldri FPGA kynslóðir

Ókostir

• Úreltur með takmarkað langtíma framboð

• Lægri rökfræði og minni getu vs. nútíma FPGA

• Hægari rekstrarhraði og I/O árangur

• Krefst ytri minni fyrir stillingar á gangi upp

• Skortir háþróaða eiginleika eins og DSP blokkir og háhraða senditæki

EP1C4F400C8 umbúðir

|

Tegund |

Færibreytur |

|

Pakkategund |

FBGA (Fine-Pitch Ball Grid fylki) |

|

Boltatölur |

400 |

|

Boltahöll (E) |

1,0 mm (dæmigert fyrir cyclone EP1C4F400) |

|

Þvermál bolta (b) |

0,45 mm (nafn) |

|

Pakkastærð (D × E) |

21 mm × 21 mm |

|

Pakkhæð (a) |

2,40 mm (max) |

|

Undirlagsþykkt (A2) |

~ 0,40 mm |

|

Þykkt moldhettu (A3) |

~ 1,90 mm |

|

Boltahæð (A1) |

0,25 mm (nafn) |

|

Pinna A1 horn |

Merkt fyrir stefnumörkun |

|

Array skipulag |

20 × 20 rist (með hornkúlur vantar) |

|

Festing |

Yfirborðsfesting (SMD) |

EP1C4F400C8 framleiðandi

EP1C4F400C8 var upphaflega framleitt af Altera Corporation, brautryðjandi í forritanlegum rökfræðibúnaði og FPGA tækni.Árið 2015 var Altera keypt af Intel Corporation, og vörulínan varð hluti af forritanlegu Solutions Group Intel (PSG).Í dag styður Intel þessi arfleifð tækjabúnað en einbeitir sér að nýrri FPGA fjölskyldum, tryggir samfellu fyrir núverandi notendur og eflir nýsköpun í forritanlegri rökfræði.

Niðurstaða

EP1C4F400C8 er áberandi sem hagkvæm og fjölhæf FPGA sem býður upp á traustan afköst fyrir miðstig hönnun.Með 4.000 rökfræðiþáttum sínum, innbyggðu minni, umfangsmiklum I/O stuðningi og eindrægni við marga spennu og viðmótsstaðla, veitir það sveigjanleika yfir fjölbreytt forrit.Arkitektúr, forritunarferli og víðtæk notagildi í DSP, innbyggðum kerfum og gagnaöflun gerir það að verklegu vali þrátt fyrir arfleifð stöðu.Þó að það skorti háþróaða eiginleika sem finnast í nýrri tækjum og frammi fyrir takmörkuðu langtíma framboði, er það áfram áreiðanlegur valkostur sem leitar sannaðra lausna í stigstærð FPGA hönnun.

DataSheet PDF

EP1C4F400C8 DATASHETS:

Um okkur

ALLELCO LIMITED

Lestu meira

Fljótur fyrirspurn

Vinsamlegast sendu fyrirspurn, við munum svara strax.

Algengar spurningar [FAQ]

1. Hvaða tæki þarf til að forrita EP1C4F400C8?

Þú þarft Quartus hugbúnað Intel (áður Altera Quartus II) ásamt studdum forritunarsnúru eins og USB-Blaster.Þessi verkfæri gera þér kleift að búa til bitastrauminn og hlaða það í FPGA.

2. Getur EP1C4F400C8 meðhöndlað PCI forrit beint?

Já, það hefur innbyggt samræmi fyrir PCI staðla (33/66 MHz, 32/64-bita), sem gerir það hentugt fyrir PCI-undirstaða samþættingu kerfisins án þess að krefjast auka brúar rökfræði.

3.. Hvað gerist ef EP1C4F400C8 mistakast við stillingar?

Ef stillingar mistakast mun conf_done pinninn ekki fullyrða hátt.Þetta bendir venjulega á villu í bitastraumsskránni, spennu raðgreiningu eða uppsetningu pinna og ætti að endurskoða það í hönnunarstreymi þínu.

4. Getur Ep1C4F400C8 tengi beint við DDR minni?

Það styður nokkra I/O staðla en er ekki með innfædd DDR tengi eins og nútíma FPGA.Nauðsynlegt er að þörf sé á viðbótarhönnunarsjónarmiðum eða brúaþáttum.

5. Hvernig ber EP1C4F400C8 saman við nýrri FPGA?

Í samanburði við nútíma tæki hefur EP1C4F400C8 minni hraða, minni rökfræðiþéttleika og færri háþróaða eiginleika.Hins vegar er það enn hagkvæmt val fyrir stöðugar, meðalstórar hönnun þar sem ekki er krafist framúrskarandi árangurs.

EPM3256AFC256-7 CPLD Yfirlit: Aðgerðir, pinout, forritun og forrit

á 2025/10/3

ADG432BR Analog Switch IC: Forskriftir, pinout, val og gagnablað

á 2025/10/2

Vinsæl innlegg

-

Flóknar tölvuuppsetningar tölvur: hvernig þær breyttu tölvunarfræði?

á 8000/04/18 147771

-

USB-C pinout og eiginleikar

á 2000/04/18 112009

-

Notkun Xilinx Unified Simulation Primitives: Alhliða leiðbeiningar um FPGA hönnun og uppgerð

á 1600/04/18 111351

-

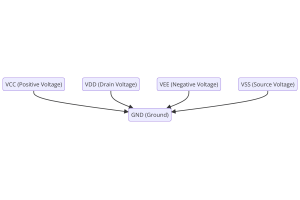

Aflgjafaspenna í rafeindatækni: Merking VCC, VDD, VEE, VSS og GND

á 0400/04/18 83768

-

RJ45 tengihandbók: Pinout, raflögn, snúrutegundir og notar

á 1970/01/1 79565

-

Endanleg leiðarvísir um vír litakóða í nútíma rafkerfum

Hvernig rafkerfin okkar nota liti er ekki bara fyrir útlit.Hver vírlitur gefur nú til kynna ákveðna aðgerð, sem gerir það auðveldara að bera kennsl á og meðhöndla rafmagn íhluta rétt við uppsetning...á 1970/01/1 66960

-

Hreinsunarhandbók: Virkni, einkenni, prófanir og skipti fyrir ákjósanlegan afköst vélarinnar

Hreinsunarventillinn er lykilatriði í kerfi bíls sem hjálpar til við að halda loftinu hreinu með því að stjórna eldsneytisgufum áður en þeir geta sloppið út í andrúmsloftið.Þetta hjálpar ekki aðein...á 1970/01/1 63098

-

Gæði (q) þáttur: jöfnur og forrit

Gæðaþátturinn, eða 'Q', er mikilvægur þegar athugað er hversu vel inductors og resonators vinna í rafrænu kerfum sem nota útvarpsbylgjur (RF).'Q' mælir hversu vel hringrás lágmarkar orkutap og hefu...á 1970/01/1 63040

-

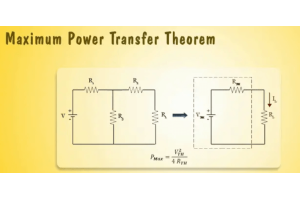

Að ná hámarksafköstum með hámarks valdaflutnings setningu

Setning hámarks aflflutnings útskýrir hvernig orka frá uppruna, svo sem rafhlöðu eða rafall, rennur til tengds álags.Það sýnir nákvæmlega ástand þar sem álagið fær mestan kraft.Þessi grein fjallar ...á 1970/01/1 54097

-

A23 rafhlöðuforskriftir og eindrægni

A23 rafhlaðan er lítil, strokkalaga rafhlaða með háspennu.Einnig kallað 23A, 23AE eða MN21, það keyrir á 12 volt og miklu hærri en AA eða AAA rafhlöður.Sérstök hönnun þess gerir það fullko...á 1970/01/1 52184