XC2C256-7TQ144C CPLD: Pinout, lögun, forritun og gagnablaðaleiðbeiningar

Í þessari handbók munt þú fá skýrt yfirlit á XC2C256-7TQ144C, lágmark CPLD frá Coolrunner-II fjölskyldu Xilinx (nú AMD).Þú munt læra um stillingar pinna, CAD módel og helstu eiginleika eins og rökfræði getu, I/O valkosti, spennu stuðning og rafmagnssparandi aðgerðir.Við munum einnig ganga í gegnum arkitektúr hans, I/V feril og forskriftir, síðan forrit, svipaðir hlutar, forritunarskref, kostir og gallar, umbúðaupplýsingar og upplýsingar framleiðanda svo þú getir skilið nákvæmlega hvernig þetta tæki passar inn í verkefnin þín.Vörulisti

Hvað er XC2C256-7TQ144C?

The XC2C256-7TQ144C er lágmark CPLD (flókið forritanlegt rökfræðibúnað) frá Coolrunner-II fjölskyldunni Xilinx, nú hluti af AMD.Það er með 256 makrókellum og er í 144 pinna TQFP pakka, hannaður fyrir hratt, ákvarðandi notkun með lágmarks orkunotkun.Með því að starfa á 1,8 V kjarna býður það upp á áreiðanlega afköst í samningur formstuðul og hentar vel fyrir hönnun sem krefst augnabliks getu og skilvirkrar útfærslu rökfræði.Sem hluti af fjölhæfu Coolrunner-II seríunni nýtur það góðs af sannaðri arkitektúr og víðtækri hönnun.

Ertu að leita að XC2C256-7TQ144C?Hafðu samband við okkur til að athuga núverandi lager, leiðslutíma og verðlagningu.

XC2C256-7TQ144C Pin-Out skýringarmynd

XC2C256-7TQ144C Pin-Out skýringarmyndin sýnir hvernig 144 pinnunum er raðað eftir krafti, jörðu, JTAG og notendaframleiðandi I/O aðgerðum.Flestir pinnar eru I/O, sem hægt er að stilla sem aðföng eða framleiðsla, og er dreift jafnt til að styðja við sveigjanlega leið.VCC, VCCIO1, VCCIO2, VAUX og GND pinnar eru settir í kringum pakkann til að bjóða upp á stöðugan afldreifingu og marga I/O spennuvalkosti.JTAG pinnar (TDI, TDO, TMS, TCK) eru flokkaðir saman til að auðvelda forritun og prófun í kerfinu.

XC2C256-7TQ144C CAD módel

XC2C256-7TQ144C tákn

XC2C256-7TQ144C fótspor

XC2C256-7TQ144C 3D líkan

XC2C256-7TQ144C eiginleikar

• Tækjutegund og fjölskylda

XC2C256-7TQ144C er flókið forritanlegt rökfræðibúnað (CPLD) sem tilheyrir Coolrunner-II fjölskyldunni sem er þróuð af Xilinx (nú AMD).Það er hannað fyrir litla orkunotkun en viðheldur hratt, ákvörðunarfræðilegri rökfræði, sem gerir það tilvalið fyrir stjórnunarrökfræði og tengiforrit.

• Rökfræði getu

Þetta tæki inniheldur 256 þjóðhagslegar, sem eru forritanleg rökfræðiauðlindir í CPLD.Hægt er að stilla þessar þjóðhagsbellur til að innleiða ýmsar samsetningar og röð rökfræðiaðgerða, sem gefur hóflega getu til að stjórna, líma rökfræði og strætóviðmót.

• Rökfræðiblokkir (aðgerðarblokkir)

Það samþættir 16 aðgerðarblokkir sem skipuleggja og stjórna hópum fjölfrumna.Hver blokk veitir staðbundna samtengingu og vöru-tímabundna auðlindir, sem gerir kleift að fá sveigjanlega rökfræði og skilvirka leið innan tækisins.

• I/O notandi pinnar

XC2C256-7TQ144C býður upp á allt að 118 notendastillanlegan I/O pinna í TQFP-144 pakkanum sínum.Þessi háa pinnaafjöldi gerir tækinu kleift að tengja við mörg undirkerfi samtímis, sem gerir það hentugt fyrir flókna hönnun á borðstigi.

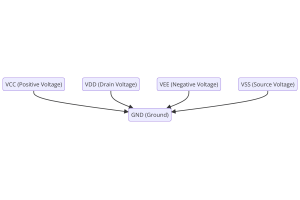

• Kjarnspenna (VCC)

Kjarninn starfar við nafn 1,8 V (1,7 V til 1,9 V svið), sem hjálpar til við að draga úr orkunotkun samanborið við eldri 5 V CPLDS.Þessi lægri spenna er gagnleg í nútíma stafrænum kerfum blandaðra spennu.

• Fjölspennu I/O stuðningur

I/O bankarnir styðja marga spennu staðla, þar á meðal 1,5 V, 1,8 V, 2,5 V og 3,3 V. Þessi sveigjanleiki gerir CPLD kleift að tengjast beint við íhluti sem starfa á mismunandi spennustigum án ytri stigs vaktara.

• Háhraða aðgerð

Með dæmigerðri útbreiðslu um útbreiðslu pinna-til-pinna, um 5,7 ns (hraða „-7“) skilar tækinu hratt, ákvarðandi afköst.Þetta gerir það hentugt fyrir tímasetningar-gagnrýnin forrit eins og afkóðun heimilisfangs, gerðardóms strætó og eftirlit.

• Lítil orkunotkun

Coolrunner-II serían er þekkt fyrir afar lága biðstrauma, oft á microamp sviðinu.Þessi lága truflanir, ásamt kraftmiklum kraftsparandi eiginleikum, gerir kleift að nota XC2C256-7TQ144C á áhrifaríkan hátt í rafhlöðuknúnu eða alltaf á kerfum.

• Gagnatækni

Þessi aðgerð gerir kleift að fara af ónotuðum aðföngum, koma í veg fyrir óþarfa að skipta um og draga úr kraftmiklum orkunotkun.Það er dýrmætt í forritum þar sem ákveðin merki eru óvirk í langan tíma.

• JATAG forritun í kerfinu

Tækið styður IEEE 1149.1 (JTAG) og IEEE 1532 fyrir forritun í kerfinu.Þetta þýðir að hægt er að stilla, prófa og endurforrita CPLD án þess að fjarlægja það af borðinu, einfalda þróun og uppfærslur.

• Háþróaður klukkuuppbygging

XC2C256-7TQ144C inniheldur margar alþjóðlegar klukkur, klukkuskiljara og tvíhliða kveikt skrár.Það veitir einnig alþjóðlegt sett/endurstillingu og staðbundna klukku á hverja þjóðhagslega, sem gefur sveigjanlega stjórn á tímasetningu og samstillingu.

• Schmitt-trigger inntak

Hægt er að stilla valinn inntakspinna sem Schmitt kallar til að bæta ónæmi fyrir hávaða.Þetta er gagnlegt til að meðhöndla hægt eða hávaðasamt inntaksmerki án þess að bæta við utanaðkomandi ástandsrásum.

• Sveigjanlegir framleiðsla eiginleikar

Framleiðslurnar styðja þriggja ríkja aðgerð, stjórnun á sveiflu, strætó, opnum tæmdum stillingum og valfrjálsum uppdrætti.Þessir valkostir gera það auðvelt að laga CPLD að ýmsum strætóstöðlum og ytri álagsskilyrðum.

• Advanced Interconnect Matrix (AIM)

Advanced Interconnect Matrix tengir virkan aðgerðarblokkir á skilvirkan hátt og veitir fulla vörutíma leið yfir tækið.Þetta bætir sveigjanleika í rökfræði og hjálpar til við að viðhalda fyrirsjáanlegum tímasetningarárangri.

Coolrunner-II CPLD arkitektúr

Coolrunner-II CPLD arkitektúr XC2C256-7TQ144C er smíðaður í kringum aðgerðarblokkir, I/O blokkir og háþróað samtengingar fylki (AIM).Hver aðgerðarblokk inniheldur þjóðhagslegar og forritanleg rökfræði (PLA) sem innleiða notendaskilgreinda rökfræði, en markmiðið skilar á skilvirkan hátt á milli blokka.I/O blokkar tengir innri rökfræði við ytri pinna og hollur JTAG og BSC/ISP rafrásir stuðnings forritun og prófun.Þessi skipulagða og samtengd arkitektúr gerir kleift að fá hratt, ákvarðandi afköst með lítilli orkunotkun, sem gerir það tilvalið fyrir stjórnun, tengi og lím rökfræði í stafrænu kerfum.

Dæmigerður I/V ferill fyrir XC2C256

Hinn dæmigerði I/V ferill fyrir XC2C256-7TQ144C sýnir sambandið milli framleiðsla spennu (VO) og framleiðsla straums (IO) fyrir mismunandi I/O framboðsspennu (1,5 V, 1,8 V, 2,5 V og 3,3 V).Þegar framboðsspenna eykst getur tækið fengið eða sökkað hærri straumum áður en framleiðsla spenna byrjar að lækka verulega.Þessi hegðun er mikilvæg til að skilja akstursgetu CPLD þegar tengist utanaðkomandi íhlutum, að tryggja að merkisstig haldist gilt undir álagi.Margir nota þennan feril til að velja viðeigandi I/O spennu og tryggja áreiðanlega notkun í forritum sem krefjast sérstakrar styrkleika núverandi aksturs.

XC2C256-7TQ144C forskriftir

|

Tegund |

Færibreytur |

|

Framleiðandi |

AMD/Xilinx |

|

Röð |

Coolrunner II |

|

Umbúðir |

Bakki |

|

Staða hluta |

Úrelt |

|

Forritanleg gerð |

Í kerfisforritanlegu |

|

Seinkaðu tíma TPD (1) Max |

6,7 ns |

|

Spennuframboð - Innra |

1,7 V ~ 1,9 V |

|

Fjöldi rökfræðiþátta/blokka |

16 |

|

Fjöldi þjóðhagsboða |

256 |

|

Fjöldi hliðar |

6000 |

|

Fjöldi i/o |

118 |

|

Rekstrarhiti |

0 ° C ~ 70 ° C (TA) |

|

Festingartegund |

Yfirborðsfesting |

|

Pakki / mál |

144-LQFP

|

|

Pakki birgjabúnaðar |

144-TQFP (20 × 20) |

|

Grunnvörunúmer |

XC2C256 |

XC2C256-7TQ144C forrit

1. lím rökfræði og tengibrúa

XC2C256-7TQ144C er tilvalið til að innleiða lím rökfræði, sem tengir og samhæfir merki milli mismunandi stafrænna íhluta.Það getur séð um aðgerðir eins og afkóðun heimilisfangs, gerðardóms strætó og þýðingu fyrir samskiptareglur, sem gerir kleift að fá slétt samskipti milli örstýringar, minni, skynjara og annarra jaðartækja.Fyrirsjáanleg tímasetning þess og hröð pinna-til-pinna tafir tryggja áreiðanlegt tengi jafnvel í flóknum borðhönnun.

2. Tæki með lágum krafti og rafhlöðu

Þökk sé Fast Zero Power (FZP) tækni og mjög lágum biðstöðu er þessi CPLD mjög hentugur fyrir flytjanlega og rafknúna rafeindatækni.Það getur verið áfram knúið stöðugt meðan það neytir lágmarks orku, sem gerir það fullkomið fyrir alltaf stjórnunar- eða eftirlitsrásir.Þú getur dregið úr orkunotkun frekar með eiginleikum eins og DataGate, sem lágmarkar kraftmikla rofa þegar aðföng eru óvirk.

3. Stjórnunarrökfræði og raðgreining

Tækið skar sig fram við að innleiða endanlegar ríkisvélar, tímasetningarstýringu og merkisröð sem krafist er í mörgum innbyggðum kerfum.Ákveðinn, óstöðugur arkitektúr þess gerir kleift að stjórna rökfræði að verða virkur strax eftir að uppstillingu er ekki hægt að nota.Þetta gerir það að sterku vali fyrir endurstillingu rökfræði, handabandsrásir og önnur tímabundin stjórnunarverkefni.

4. innbyggður kerfisstuðningur og útlæga rökfræði

Í innbyggðum hönnun getur XC2C256-7TQ144C virkað sem sérsniðinn stuðningsflís, innleiða sérhæfð tengi eða lengja getu örstýringar.Það ræður við samskiptareglur eins og SPI, I²C eða UART, búið til flísval eða stjórnað truflunarleið.Með því að hlaða þessum aðgerðum frá CPU einfaldar það þróun vélbúnaðar og bætir árangur kerfisins.

XC2C256-7TQ144C Svipaðir hlutar

|

Forskrift |

XC2C256-7TQ144C |

XC2C256-7TQ144I |

XC2C256-7TQG144I |

XC2C256-7VQ100C |

XC2C256-7VQG100C |

XC2C256-6TQ144C |

|

Tækifjölskylda |

Coolrunner-II Cpld |

Coolrunner-II Cpld |

Coolrunner-II Cpld |

Coolrunner-II Cpld |

Coolrunner-II Cpld |

Coolrunner-II Cpld |

|

Rökþéttleiki (þjóðhagslegir) |

256 |

256 |

256 |

256 |

256 |

256 |

|

Pakkategund |

TQFP-144 |

TQFP-144 |

TQFP-144 (PB-Free) |

VQFP-100 |

VQFP-100 (PB-Free) |

TQFP-144 |

|

Hraða bekk |

-7 |

-7 |

-7 |

-7 |

-7 |

-6 (hraðari) |

|

Hitastigssvið |

Auglýsing (0 - 70 ° C) |

Iðnaðar (-40-85 ° C) |

Iðnaðar (-40-85 ° C) |

Auglýsing (0 - 70 ° C) |

Auglýsing (0 - 70 ° C) |

Auglýsing (0 - 70 ° C) |

|

I/O Pin fjöldi |

118 |

118 |

118 |

80 |

80 |

118 |

|

Kjarnspenna (VCC) |

1,8 V. |

1,8 V. |

1,8 V. |

1,8 V. |

1,8 V. |

1,8 V. |

|

I/O spennustuðningur |

1,5 V - 3,3 V |

1,5 V - 3,3 V |

1,5 V - 3,3 V |

1,5 V - 3,3 V |

1,5 V - 3,3 V |

1,5 V - 3,3 V |

|

Fylgni / PB-frjáls |

Standard |

Standard |

PB-Free / Rohs |

Standard |

PB-Free / Rohs |

Standard |

|

Munur |

Upphafsútgáfa í upphafi |

Iðnaðar tempútgáfa |

Industrial + Pb-frjáls útgáfa |

Minni pakki, færri I/O |

PB-frjáls minni útgáfa |

Hraðari tímasetningarútgáfa |

XC2C256-7TQ144C forritunarskref

Forritun XC2C256-7TQ144C er einfalt ferli sem felur í sér að undirbúa hönnun þína, búa til forritunarskrána og hlaða hana í CPLD í gegnum JTAG.Með því að fylgja hverju skrefi vandlega geturðu tryggt árangursríka stillingu og rétta tæki á borðinu.

1. hönnun og samstillt

Þú byrjar á því að skrifa rökfræðihönnun þína með HDL (VHDL eða Verilog) eða skýringarmynd.Eftir að hafa lokið hönnuninni keyrir þú myndunarferlið, sem breytir rökfræði þinni í innri uppbyggingu tækisins á þjóðhagsbellum og samtengingum.Þetta skref tryggir að hönnun þín sé samhæf við XC2C256 arkitektúrinn og tilbúin til framkvæmdar.

2. Staður og leið / útfærsla (mátun)

Næst framkvæmir þú stað og leið, einnig þekktur sem mátun, sem úthlutar samstillta rökfræði þinni til raunverulegra líkamlegra þjóðhagsboða og leiðarauðlinda inni í CPLD.Tólið athugar tímasetningartakmarkanir, leysir notkun auðlinda og hámarkar slóðir til að mæta afköstum hönnunarinnar.Þetta tryggir að hringrásin mun keyra áreiðanlega einu sinni forritað í tækið.

3. Búðu til forritunarskrá

Þegar útfærslunni er lokið býrðu til forritunarskrána (bit, sultu eða SVF snið) sem inniheldur nákvæm stillingargögn fyrir tækið.Þessi skrá táknar hvernig hver þjóðhagsleg, samtenging og I/O er sett upp til að útfæra rökfræði þína.Það er þörf á þessari skrá tilbúna áður en haldið er áfram í raunverulega forritun tækisins.

4. JTAG / forritun í kerfinu

Að lokum tengir þú tækið við tölvuna þína með JTAG forritunarsnúru og opnar Xilinx Impact tólið (eða samsvarandi).Þú hleður síðan myndaða forritunarskránni og halar henni niður á XC2C256-7TQ144C í gegnum JTAG pinna (TDI, TDO, TCK, TMS).Þegar ferlinu er lokið byrjar CPLD strax að starfa með forritaðri rökfræði án þess að þurfa rafmagnsferil eða ytri stillingarminni.

XC2C256-7TQ144C Kostir og gallar

Kostir

• Mjög lágt í biðstöðu, tilvalið fyrir rafhlöðuknúna hönnun.

• Augnablik aðgerð án seinkunar á stillingum.

• Fyrirsjáanleg tímasetning fyrir auðveldari lokun hönnunar.

• Skiptir um margar stakar röksemdaflísir, sparar rými og kostnað.

• Styður marga I/O spennu án ytri stigs vaktar.

Ókostir

• Takmörkuð rökfræði getu miðað við stærri CPLD eða FPGA.

• Engin innbyggð DSP, vinnsluminni eða háhraða senditæki.

• Að verða úreltur, gera framtíðarkaup erfiðara.

• Lægra afköst loft fyrir háhraða forrit.

• Minni sveigjanleiki fyrir flókna eða óreglulega hönnun.

XC2C256-7TQ144C umbúðir víddir

|

Tegund |

Færibreytur |

|

Pakkategund |

TQFP-144 |

|

Líkamsstærð pakka |

20 mm × 20 mm |

|

Aðalhæð |

0,5 mm |

|

Fjöldi pinna |

144 |

|

Pakkhæð (Max) |

1,4 mm |

|

Pakkþykkt (nafn) |

1,0 mm |

|

Blýlengd |

0,45 mm ~ 0,75 mm |

|

Blýbreidd |

0,17 mm ~ 0,27 mm |

|

Festingartegund |

Yfirborðsfesting |

|

Pakki birgjabúnaðar |

144-TQFP (20 × 20) |

XC2C256-7TQ144C framleiðandi

XC2C256-7TQ144C er framleitt með Xilinx, leiðandi fyrirtæki í forritanlegum rökfræðilegum lausnum.Xilinx er víða viðurkennt fyrir brautryðjandi FPGA og CPLD tækni, sem veitir áreiðanlegar og afkastamikil tæki fyrir atvinnu-, atvinnu- og neytendaforrit.Í dag starfar Xilinx sem hluti af Amd, Haltu áfram að skila háþróuðum forritanlegum rökum með sterkum langtíma stuðningi og nýsköpun.

Niðurstaða

XC2C256-7TQ144C er áberandi fyrir litla orkunotkun sína, hröð ákvarðandi afköst og fjölspennu I/O sveigjanleika, sem gerir það að áreiðanlegu vali fyrir nútíma stafræna hönnun.Jafnvægi samsetning þess af 256 makrósellum, 118 I/O pinna og háþróaðri samtengisarkitektúr styður breitt svið stjórnunar, tengi og lím rökfræði.Með stuðningi við forritun í kerfinu, DataGate Power sparandi eiginleikum og öflugum I/O stillingum, þá samþættir það vel í innbyggð kerfi og blandað spennuumhverfi.

DataSheet PDF

XC2C256-7TQ144C DataSeets:

Um okkur

ALLELCO LIMITED

Lestu meira

Fljótur fyrirspurn

Vinsamlegast sendu fyrirspurn, við munum svara strax.

Algengar spurningar [FAQ]

1.

Nei. Einn af kostum þess er strax í notkun.Stillingin er geymd innbyrðis, þannig að hún gerir það tilbúið til að keyra án utanaðkomandi prom eða leifturminni.

2. Hvaða forritunartæki eru samhæf við XC2C256-7TQ144C?

Þú getur forritað tækið með Xilinx Impact hugbúnaði með JTAG forritunarsnúru.Margir nota einnig samhæfða JTAG forritara þriðja aðila, en vertu viss um að þeir styðji IEEE 1149.1/1532 staðla.

3. Getur XC2C256-7TQ144C skipt um margar stakar rökfræði í hönnun þinni?

Já.Með 256 makrókellum sínum og sveigjanlegum I/O, getur þetta CPLD samþætt nokkrar lím rökfræði og stjórnunaraðgerðir í eitt tæki og hjálpað þér að draga úr borðrými og íhlutafjölda.

4. Er XC2C256-7TQ144C hentugur fyrir rafhlöðuforrit með lágum krafti?

Já.Þökk sé Fast Zero Power (FZP) tækni og mjög lágum biðstöðu er það tilvalið fyrir alltaf hringrás, flytjanleg tæki og valdnæmt innbyggð kerfi.

5. Getur þú notað XC2C256-7TQ144C til að vinna með háhraða merkis?

Það er ekki hannað fyrir háhraða DSP eða senditæki.Þó að það skili hröðum töfum til pinna, þá hentar það best fyrir stjórnun, tengi og tímasetningu, ekki flókna gagnavinnslu.

EP2S60F672C4 FPGA: Aðgerðir, forrit, forritun og gagnablaðaleiðbeiningar

á 2025/10/4

EPM3256AFC256-7 CPLD Yfirlit: Aðgerðir, pinout, forritun og forrit

á 2025/10/3

Vinsæl innlegg

-

Flóknar tölvuuppsetningar tölvur: hvernig þær breyttu tölvunarfræði?

á 8000/04/19 147781

-

USB-C pinout og eiginleikar

á 2000/04/19 112056

-

Notkun Xilinx Unified Simulation Primitives: Alhliða leiðbeiningar um FPGA hönnun og uppgerð

á 1600/04/19 111352

-

Aflgjafaspenna í rafeindatækni: Merking VCC, VDD, VEE, VSS og GND

á 0400/04/19 83810

-

RJ45 tengihandbók: Pinout, raflögn, snúrutegundir og notar

á 1970/01/1 79624

-

Endanleg leiðarvísir um vír litakóða í nútíma rafkerfum

Hvernig rafkerfin okkar nota liti er ekki bara fyrir útlit.Hver vírlitur gefur nú til kynna ákveðna aðgerð, sem gerir það auðveldara að bera kennsl á og meðhöndla rafmagn íhluta rétt við uppsetning...á 1970/01/1 66995

-

Hreinsunarhandbók: Virkni, einkenni, prófanir og skipti fyrir ákjósanlegan afköst vélarinnar

Hreinsunarventillinn er lykilatriði í kerfi bíls sem hjálpar til við að halda loftinu hreinu með því að stjórna eldsneytisgufum áður en þeir geta sloppið út í andrúmsloftið.Þetta hjálpar ekki aðein...á 1970/01/1 63119

-

Gæði (q) þáttur: jöfnur og forrit

Gæðaþátturinn, eða 'Q', er mikilvægur þegar athugað er hversu vel inductors og resonators vinna í rafrænu kerfum sem nota útvarpsbylgjur (RF).'Q' mælir hversu vel hringrás lágmarkar orkutap og hefu...á 1970/01/1 63057

-

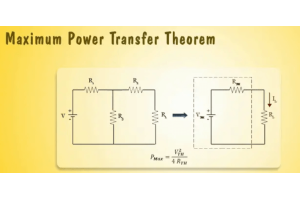

Að ná hámarksafköstum með hámarks valdaflutnings setningu

Setning hámarks aflflutnings útskýrir hvernig orka frá uppruna, svo sem rafhlöðu eða rafall, rennur til tengds álags.Það sýnir nákvæmlega ástand þar sem álagið fær mestan kraft.Þessi grein fjallar ...á 1970/01/1 54097

-

A23 rafhlöðuforskriftir og eindrægni

A23 rafhlaðan er lítil, strokkalaga rafhlaða með háspennu.Einnig kallað 23A, 23AE eða MN21, það keyrir á 12 volt og miklu hærri en AA eða AAA rafhlöður.Sérstök hönnun þess gerir það fullko...á 1970/01/1 52207