EP20K100EFC324-1X FPGA: Aðgerðir, forskriftir, forrit og forritunarleiðbeiningar

EP20K100EFC324-1X er forritanlegur flís (FPGA) úr Intel's Altera Apex-20Ke® seríunni.Það er hannað til að takast á við flóknar stafrænar hringrásir og styður háhraða gagnavinnslu.Þessi handbók útskýrir eiginleika sína, forskriftir, hvernig á að forrita það og kosti þess, sem gerir það að gagnlegu úrræði fyrir alla.Vörulisti

EP20K100EFC324-1X yfirlit

The EP20K100EFC324-1X er hluti af Altela Apex-20K® seríunni Intel, sviði forritanleg Gate Array (FPGA) sem er sérsniðin fyrir háþéttni forritanleg rökfræðiforrit sem krefjast háþróaðra kerfis-á-A-forritanlegra flísar (SOPC) samþættinga.Þetta tæki er aðgreint með samþættingu þess á 4.160 rökfræðiþáttum eða frumum og 416 rökfræðiblokkum (Labs), sem auðveldar verulegan stillanleika fyrir ýmsa hönnun stafrænna hringrásar.Það státar einnig af töluverðu magni af innbyggðu minni sem rúmar kröfur um gagna geymslu innan FPGA.EP20K100EFC324-1X, sem er ennfremur aukið fjölhæfni þess, styður 246 I/O pinna og býður upp á verulega hliðatalningu um það bil 263.000 samsvarandi hlið, sem starfa á skilvirkan hátt á milli 1,71V til 1,89V.Það er pakkað í 324 ball fínpitakúlukúlurit (FBGA), sem hjálpar til við öfluga líkamlega samþættingu í rafrænum samsetningum.

EP20K100EFC324-1X er hið fullkomna val þegar þú ert tilbúinn að setja magnpantanir hjá okkur fyrir verkefnin þín eða vörulínur.

EP20K100EFC324-1X CAD módel

EP20K100EFC324-1X tákn

EP20K100EFC324-1X fótspor

EP20K100EFC324-1X 3D líkan

EP20K100EFC324-1X aðgerðir

• Hár rökfræðiþéttleiki: FPGA er búinn 4.160 rökfræðiþáttum (LES) og 416 Logic Array Blocks (Labs).Þessi mikli þéttleiki rökfræðifrumna gerir ráð fyrir hönnun og framkvæmd flókinna stafrænna hringrásar og kerfa innan eins flísar, sem gerir það tilvalið fyrir forrit sem krefjast öflugs vinnslugetu.

• Innbyggt minni: Bjóða 53.248 RAM bita, þessi FPGA veitir umtalsverðar innbyggðar minnisauðlindir.Þessi eiginleiki er góður fyrir forrit sem krefjast skjótra gagnageymslu og sóknar, sem gerir kleift að meðhöndla gagnafrek verkefni.

• Umfangsmikil I/O getu: Með 246 inntak/úttakspinna tryggir EP20K100EFC324-1X alhliða tengingu og tengivalkosti.Þetta breitt svið I/O getu gerir honum kleift að tengjast auðveldlega með fjölmörgum utanaðkomandi tækjum og kerfum og auka notagildi þess í flóknum rafrænum samsetningum.

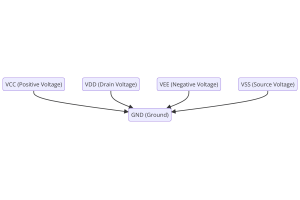

• Fjölspennustuðningur: Tækið styður grunnspennu svið 1,71V til 1,89V og er með Multivolt ™ I/O tengi.Þetta gerir FPGA kleift að vera samhæft við aðra rafeinda hluti sem starfa á ýmsum rökfræði, þar á meðal 1,8V, 2,5V, 3,3V og 5,0V, sem veitir mikinn sveigjanleika í kerfishönnun.

EP20K100EFC324-1X blokkarmynd

The EP20K100EFC324-1X blokkarmynd Táknar innra uppbyggingu FPGA (Field Programmeble Gate Array) tæki og sýnir ýmsar hagnýtar einingar þess.Skýringarmyndin samanstendur af samtengdum rökfræðiblokkum, minniþáttum, klukkustjórnun og I/O þáttum.Kjarni hönnunarinnar eru Rökfræði fylkisblokkir (Rannsóknarstofur), sem innihalda Flettu upp borðum (LUTS) og rökfræði sem byggir á vöru.Þessir þættir leyfa sveigjanlega rökfræði útfærslu, sem gerir FPGA hentugt fyrir háhraða stjórnunarrökfræði, ríkisvélar og DSP aðgerðir.The FastTrack samtenging Veitir háhraða samskiptabraut milli rökfræðiþátta, sem tryggir skilvirka merkisleiðslu um allt tækið.The Klukkustjórnunarrásir , þar með talið Clocklock aðgerðin, tryggir áreiðanlega og samstillta notkun með því að koma á stöðugleika og dreifa klukkutegundum yfir FPGA.The Inntak/úttaksþættir (IOES), staðsett í kringum FPGA efnið, þjóna sem tengi fyrir utanaðkomandi samskipti.Þessir iOes styðja margar iðnaðarstaðalar samskiptareglur eins og PCI, GTL+, SSTL-3, og LVDS, sem gerir FPGA kleift að tengja við margs konar ytri kerfi.Þessir IOE tryggir eindrægni við mismunandi spennustig og merkjaslóð og eykur fjölhæfni FPGA í innbyggðum forritum. Innbyggð minni blokkir Búðu til sveigjanlegar geymslulausnir innan FPGA.Þessir minniþættir geta virkað sem Innihald sem hægt er að takast á við (Cam), Handahófi aðgangs minni (RAM), Lestur-aðeins minni (Róm), Fyrsta-í-fyrsta-út (FIFO) Buffarar og önnur minni mannvirki.Hæfni til að samþætta minni beint innan FPGA efnisins bætir skilvirkni gagnavinnslu, dregur úr utanaðkomandi minni ósjálfstæði og leynd.

EP20K100EFC324-1X forskriftir

|

Tegund |

Færibreytur |

|

Framleiðandi |

Intel |

|

Röð |

Apex-20Ke® |

|

Umbúðir |

Bakki |

|

Staða hluta |

Úrelt |

|

Fjöldi rannsóknarstofna/CLB |

416 |

|

Fjöldi rökfræðiþátta/frumna |

4160 |

|

Heildar vinnsluminni |

53248 |

|

Fjöldi i/o |

246 |

|

Fjöldi hliðar |

263000 |

|

Spenna - framboð |

1,71V ~ 1,89V |

|

Festingartegund |

Yfirborðsfesting |

|

Rekstrarhiti |

0 ° C ~ 85 ° C (TJ) |

|

Pakki / mál |

324-BGA |

|

Pakki birgjabúnaðar |

324-fbga (19x19) |

|

Grunnvörunúmer |

EP20K100 |

EP20K100EFC324-1X forrit

Net og samskipti

Þessi FPGA er tilvalin fyrir netbúnað eins og beina og rofa, þar sem það stýrir gagnaleið, merkisvinnslu og meðhöndlun samskiptareglna.Hár rökfræðiþéttleiki þess og umfangsmikil I/O getu gerir það kleift að styðja flókna, háhraða gagnaaðgerðir sem krafist er í nútíma samskiptainnviði.

Iðnaðareftirlitskerfi

Í iðnaðargeiranum er EP20K100EFC324-1X framúrskarandi í sjálfvirkni kerfum.Forritunarhæfni þess og öflug vinnslugeta gerir kleift að ná nákvæmri stjórnun og eftirliti til að auka skilvirkni og áreiðanleika í framleiðsluferlum.

Bifreiðar rafeindatækni

FPGA þjónar sem hluti í bifreiðaforritum, sérstaklega í háþróaðri ökumannsaðstoðarkerfi (ADAS) og infotainment kerfi í ökutæki.Það veitir nauðsynlegan vinnsluorku og aðlögunarhæfni til að takast á við gögn og styðja við háþróaða virkni sem krafist er í nútíma ökutækjum.

Rafeindatækni neytenda

Vegna sveigjanleika og afkastamikils er EP20K100EFC324-1X einnig að finna í neytandi rafeindatækni eins og háskerpu sjónvörpum og leikjatölvum.Það styður flókna virkni og hjálpartæki við styttingu vöruþróunar og uppfyllir hraðskreyttan eftirspurn eftir neytendafræðumarkaðnum.

Lækningatæki

Á læknisfræðilegum vettvangi stuðlar þessi FPGA að virkni læknisfræðilegra myndatöku og greiningartækja.Geta þess til að vinna úr gögnum á miklum hraða tryggir að þessi tæki geta skilað nákvæmum og tímabærum greiningarniðurstöðum fyrir árangursríka læknismeðferð og myndgreiningu.

EP20K100EFC324-1X Svipaðir hlutar

EP20K100EFC324-1X forritunarskref

Til að forrita á áhrifaríkan hátt EP20K100EFC324-1X, meðlimur í Apex-20Ke® FPGA seríunni Altera, er mikilvægt að fylgja skipulagðri röð af skrefum.Þetta ferli tryggir að hönnun þín er skilvirkt þýtt á snið sem FPGA getur framkvæmt.Hér að neðan geri ég grein fyrir ítarlegri nálgun til að forrita þetta FPGA líkan, samþætta skref og breytingar sem eru sértækar fyrir þetta tæki.

1. Hönnunarfærsla

Byrjaðu á því að búa til stafræna rökfræði hönnun þína.Notaðu vélbúnaðarlýsingu tungumál (HDL) eins og VHDL eða Verilog, sem gerir þér kleift að lýsa vélbúnaðarvirkni og rökfræði kerfisins.Verkfæri eins og Altera's Quartus II bjóða upp á yfirgripsmikið umhverfi til að skrifa, prófa og setja saman HDL kóða.Gakktu úr skugga um að hönnun þín sé mát, sem gerir það auðveldara að kemba og kvarða.

2. Synthesis

Þegar hönnunarfærslunni þinni er lokið er næsta skref nýmyndun, þar sem HDL kóðinn er þýddur á netlista.Þessi netlisti táknar samtengda lista yfir hlið, flip-flops og aðra vélbúnaðarþætti sem mynda hönnun þína.Við myndun er kóðinn fínstilltur fyrir sérstaka arkitektúr EP20K100EFC324-1X og tryggir að hönnunin nýti auðlindir FPGA á áhrifaríkan hátt.Hægt er að nota verkfæri eins og Synplay Pro eða Synthesis tólið innan Quartus II í þessum tilgangi.Það er mikilvægt að einbeita sér að því að hámarka hönnun þína til að uppfylla tímasetningu og auðlindir.

3. Framkvæmd

Eftir myndun fer fram framkvæmd.Þetta skref felur í sér að kortleggja netlistann á raunverulegum FPGA vélbúnaði.Það felur í sér staðsetningu rökfræðiþátta innan FPGA og leiðar tengingarnar á milli.Quartus II hugbúnaðurinn auðveldar þetta ferli með útfærsluverkfærum sínum, sem stjórna staðsetningu og leið til að uppfylla viðkomandi klukkuhraða og árangursmælikvarða.Meðan á framkvæmd stendur gætirðu þurft að endurtaka hönnun þína út frá endurgjöf frá tímasetningargreiningartækjum til að tryggja að allar frammistöðukröfur séu uppfylltar.

4. Bitstream kynslóð

Eftir árangursríka framkvæmd er næsti áfangi að búa til bitastrauminn.Þetta er tvöfaldur skrá sem verður hlaðin á FPGA.Bitstream inniheldur stillt gögn fyrir hvern forritanlegan þátt í FPGA og setur upp tækið til að framkvæma aðgerðirnar samkvæmt hönnun þinni.Quartus II hugbúnaðurinn getur búið til þennan bitastraum, sem síðan er tilbúinn til að hlaða niður á FPGA.

5. Forritun FPGA

Lokaskrefið er að forrita FPGA með myndaðri bitastraumi.Þetta er hægt að gera með vélbúnaðar forritara sem er samhæfur við EP20K100EFC324-1X, svo sem USB Blaster.Tengdu forritarann við þróunarborðið þitt þar sem FPGA er festur og notaðu Quartus II forritara tólið til að flytja bitastrauminn yfir í FPGA.Þetta skref mun hlaða hönnun þína á FPGA og það mun byrja að starfa samkvæmt röksemdafærslunni sem skilgreind er í HDL kóðanum þínum.

EP20K100EFC324-1X Kostir

Mikil samþætting

EP20K100EFC324-1X býður upp á mikla samþættingargetu vegna mikils fjölda rökfræðiþátta og innbyggðs minni.Þessi samþætting gerir kleift að sameina margvíslegar virkni í eitt tæki.Fyrir vikið er hægt að einfalda kerfin, draga úr heildarafkomu íhluta, líkamlegu rými og mögulegum bilunarstigum í rafrænum hönnun.

Sveigjanleg framkvæmd rökfræði

Arkitektúr EP20K100EFC324-1X styður bæði uppflettitöflu (LUT) og vöru sem byggir á vöru.Þessi sveigjanleiki í útfærslu rökfræði gerir kleift að hámarka FPGA fyrir fjölbreytt úrval af forritum, allt frá einföldum rökum hliðum til flókinna samsettra hringrásar.Það veitir forskot hvað varðar fjölhæfni hönnunar og getur komið til móts við breitt svið stafrænna virkni.

Háþróuð samtenging uppbygging

FPGA er með stigveldi samtengingar uppbyggingu og inniheldur samtengingar Local, Megalab ™ og FastTrack®.Þessar sérhæfðu leiðarauðlindir auka skilvirkni merkja og bæta heildarafköst tækisins.Þessi háþróaða samtenging er góð fyrir hönnun sem krefst háhraða gagnaflutnings og lítillar leynd, sem gerir FPGA tilvalið fyrir afkastamikla tölvunarfræði og fjarskipti.

Klukkustjórnun

EP20K100EFC324-1X felur í sér Clocklock og ClockBoost tækni, sem hjálpar til við árangursríka klukkustjórnun.Þessir eiginleikar hjálpa til við að viðhalda heiðarleika klukku merkisins um allt FPGA, draga úr jitter og bæta áreiðanleika merkja.Árangursrík klukkustjórnun er nauðsynleg fyrir samstilltar stafrænar hringrásir, sem tryggja stöðugan og fyrirsjáanlegan rekstur við ýmsar umhverfisaðstæður.

Hönnun sveigjanleika

Forritanlegt eðli EP20K100EFC324-1X gerir kleift að sníða vélbúnað að sérstökum þörfum og endurstilla FPGA fyrir mismunandi forrit eða uppfærslur.Þessi sveigjanleiki þýðir að hægt er að nota eitt FPGA í mörgum verkefnum, sem er gagnlegt í öflugu tæknilegu landslagi þar sem kröfur geta breyst hratt.

Hröð frumgerð

FPGA eins og EP20K100EFC324-1X gerir kleift að fá skjót frumgerð af stafrænum hringrásum.Þú getur þróað og endurtekið hönnun fljótt án langra leiðartíma sem tengjast sérsniðnum ASIC þróun.Þessi geta til að móta og prófa nýja hönnun fljótt flýtir fyrir þróunarferlinu, sem leiðir til hraðari nýsköpunar og styttra tíma til markaðar.

Kostnaðar skilvirkni

Að samþætta margar aðgerðir innan eins FPGA dregur úr þörfinni fyrir viðbótar stakir íhlutir, sem geta leitt til kostnaðarsparnaðar bæði í innkaupum og samsetningu.Þessi samþætting einfaldar einnig framleiðsluferlið og getur dregið úr heildstigi kerfisins, sem leiðir til minni viðhalds og uppfærslukostnaðar yfir líftíma vörunnar.

Langtíma stuðningur

Endurstillanlegur þáttur EP20K100EFC324-1X tryggir að hægt sé að uppfæra vélbúnað til að laga villur, bæta árangur eða bæta við nýjum eiginleikum án þess að krefjast líkamlegra breytinga á vélbúnaði.Þessi langtíma stuðningur og aðlögunarhæfni vernda fjárfestingar og gerir tækjum kleift að vera viðeigandi þegar nýir staðlar og tækni koma fram.

EP20K100EFC324-1X umbúðir

EP20K100EFC324-1X er FPGA frá Apex-20K® röð Altera, til húsa í a 324-ball Fine-Pitch Ball Grid Array (FBGA) pakki.Umbúðir þess eru eftirfarandi:

• Pitch: 1 mm

• Lengd × breidd: 19 mm × 19 mm

• Svæði: 361 mm²

EP20K100EFC324-1X framleiðandi

EP20K100EFC324-1X er líkan úr Apex-20Ke® röð af reitum forritanlegum hliðar fylki (FPGA) sem upphaflega var þróað af Altera.Eftir kaup Intel á Altera árið 2015 urðu þessi FPGA og aðrar Altera vörur hluti af umfangsmiklu forritanlegu lausnum Intel.Fyrir vikið, Intel heldur áfram að styðja vörulínur Altera og samþætta þær með eigin háþróaðri tækniframboði.Þrátt fyrir að EP20K100EFC324-1X hafi verið flokkað sem úrelt og er ekki lengur í framleiðslu, er arfleifð þess haldið undir Intel, sem mælir með nýrri FPGA líkönum fyrir núverandi forrit til að tryggja langtíma stuðning og framboð.

Niðurstaða

EP20K100EFC324-1X er öflugur og sveigjanlegur FPGA sem gerir kleift að búa til og prófa sérsniðnar stafrænar hringrásir.Það býður upp á afköst, innbyggt minni og fjölspennu stuðning, sem gerir það gagnlegt í mörgum atvinnugreinum.Þessi handbók hefur tekið þig í gegnum helstu eiginleika, hönnun og skref til að forrita þennan FPGA á einfaldan hátt, svo þú getur auðveldlega skilið og notað hann.

DataSheet PDF

EP20K100EFC324-1X DATASHETS:

Um okkur

ALLELCO LIMITED

Lestu meira

Fljótur fyrirspurn

Vinsamlegast sendu fyrirspurn, við munum svara strax.

Algengar spurningar [FAQ]

1.

EP20K100EFC324-1X er áfram öflug FPGA fyrir arfakerfi og iðnaðarforrit sem krefjast mikils rökfræðiþéttleika og sveigjanlegra I/O getu.Samt sem áður, samanborið við nútíma FPGA eins og Cyclone, Arria eða Stratix röð Intel, skortir það háþróaða orkunýtni, háhraða senditæki og AI-ekna hröðun.Ef þú ert að hanna nýtt kerfi getum við stungið upp á jafngildum eða uppfærðum gerðum.

2.. Styður EP20K100EFC324-1X ytri minni tengi eins og DDR eða SRAM?

Já, EP20K100EFC324-1X styður ytri minni tengi, þar á meðal SRAM og SDRAM.Hins vegar styður það ekki náttúrulega DDR2/DDR3.Ef þörf er á háhraða minni viðmóti gæti verið nauðsynlegt viðbótar ytri rökfræði eða nýrri FPGA.

3. Get ég endurstillt EP20K100EFC324-1X margfalt?

Já, eins og öll FPGA, þá er þetta tæki að fullu endurgjöf.Hins vegar, ef þú notar rokgjörn stillingu, þarftu hins vegar ytri minni (svo sem raðpall) til að halda hönnuninni eftir orkuhjólreiðum.

4. Get ég forritað EP20K100EFC324-1X með Intel Quartus hugbúnaði?

Já, þú getur forritað EP20K100EFC324-1X með Intel Quartus II (Legacy útgáfur), þar sem þessi FPGA tilheyrir Apex-20Ke® fjölskyldunni.Gakktu úr skugga um að Quartus II útgáfan þín styðji þetta tæki, þar sem nýrri Quartus Prime Editions styður ekki Legacy FPGA.

5. Hvaða aflgjafaþörf ætti ég að íhuga þegar ég nota EP20K100EFC324-1X?

EP20K100EFC324-1X starfar með grunnspennu svið 1,71V til 1,89V.Það er einnig með Multivolt ™ I/O tækni, styður 1,8V, 2,5V, 3,3V og 5,0V rökfræði.Gakktu úr skugga um að aflgjafinn þinn uppfylli þessar spennukröfur fyrir stöðugan afköst.

XCV200-6FG456C FPGA: Aðgerðir, forskriftir, forritun og forrit

á 2025/03/20

Af hverju 0603 íhlutir eru vinsælir í nútíma rafeindatækni

á 2025/03/20

Vinsæl innlegg

-

Flóknar tölvuuppsetningar tölvur: hvernig þær breyttu tölvunarfræði?

á 8000/04/18 147770

-

USB-C pinout og eiginleikar

á 2000/04/18 112006

-

Notkun Xilinx Unified Simulation Primitives: Alhliða leiðbeiningar um FPGA hönnun og uppgerð

á 1600/04/18 111351

-

Aflgjafaspenna í rafeindatækni: Merking VCC, VDD, VEE, VSS og GND

á 0400/04/18 83768

-

RJ45 tengihandbók: Pinout, raflögn, snúrutegundir og notar

á 1970/01/1 79562

-

Endanleg leiðarvísir um vír litakóða í nútíma rafkerfum

Hvernig rafkerfin okkar nota liti er ekki bara fyrir útlit.Hver vírlitur gefur nú til kynna ákveðna aðgerð, sem gerir það auðveldara að bera kennsl á og meðhöndla rafmagn íhluta rétt við uppsetning...á 1970/01/1 66959

-

Hreinsunarhandbók: Virkni, einkenni, prófanir og skipti fyrir ákjósanlegan afköst vélarinnar

Hreinsunarventillinn er lykilatriði í kerfi bíls sem hjálpar til við að halda loftinu hreinu með því að stjórna eldsneytisgufum áður en þeir geta sloppið út í andrúmsloftið.Þetta hjálpar ekki aðein...á 1970/01/1 63098

-

Gæði (q) þáttur: jöfnur og forrit

Gæðaþátturinn, eða 'Q', er mikilvægur þegar athugað er hversu vel inductors og resonators vinna í rafrænu kerfum sem nota útvarpsbylgjur (RF).'Q' mælir hversu vel hringrás lágmarkar orkutap og hefu...á 1970/01/1 63040

-

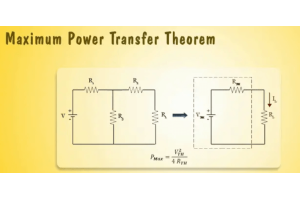

Að ná hámarksafköstum með hámarks valdaflutnings setningu

Setning hámarks aflflutnings útskýrir hvernig orka frá uppruna, svo sem rafhlöðu eða rafall, rennur til tengds álags.Það sýnir nákvæmlega ástand þar sem álagið fær mestan kraft.Þessi grein fjallar ...á 1970/01/1 54095

-

A23 rafhlöðuforskriftir og eindrægni

A23 rafhlaðan er lítil, strokkalaga rafhlaða með háspennu.Einnig kallað 23A, 23AE eða MN21, það keyrir á 12 volt og miklu hærri en AA eða AAA rafhlöður.Sérstök hönnun þess gerir það fullko...á 1970/01/1 52182