XCV200-6FG456C FPGA: Aðgerðir, forskriftir, forritun og forrit

XCV200-6FG456C er öflugur FPGA (Field-forritanlegt Gate Array) frá AMD Xilinx Virtex® seríunni.Þessi handbók útskýrir eiginleika sína, PIN -skipulag, forritunarskref og notkun.Með mikilli vinnsluorku, sveigjanlegum hönnunarmöguleikum og sterkum inntak/framleiðsla (I/O) getu, hjálpar þessi FPGA að byggja upp hratt og áreiðanlegt stafræn kerfi.Hvort sem þú ert að vinna í netkerfi, stjórnkerfi eða sérsniðnum rafeindatækni, þá mun þessi handbók hjálpa þér að skilja hvernig hægt er að nota XCV200-6FG456C í verkefnum þínum.Vörulisti

XCV200-6FG456C yfirlit

The XCV200-6FG456C er athyglisverð líkan innan AMD Xilinx Virtex® FPGA fjölskyldunnar, sem er hönnuð til að bjóða upp á öflugar forritanlegar rökfræðilegar lausnir fyrir flókin stafræn kerfi.Þessi sérstaka flís nær yfir 236.666 kerfishlið og er með 1.176 stillanlegar rökfræðiblokkir (CLB) og 5.292 rökfræðifrumur.Það felur einnig í sér 57.344 heildar vinnsluminni og stoð 284 I/O pinna, til húsa í 456 ball fínpitakúlukúlupakka (FBGA) pakka, sem mælir 23mm x 23mm.Þetta líkan starfar á 2,5V nafnspennu, á bilinu 2,375V til 2,625V, og getur virkað innan hitastigs 0 ° C til 85 ° C.Víðtækari Virtex® serían sér um ýmis forrit með þéttleika frá 50.000 í yfir 1 milljón kerfishlið og kerfis klukkuhraða allt að 200 MHz.Það styður fjölmarga I/O staðla þar á meðal LVTTL, LVCMOS og PCI, meðal annarra.Eiginleikar eins og seinkunarlykkjur (DLLs), stillanleg rökfræðiblokkir með innbyggðu minni og hollur burðarrökfræði fyrir tölur um aðgerðir auka virkni þess.Virtex® fjölskyldan tryggir afköst og áreiðanleika með því að nota 0,22 µm 5 lag málmferlið.

Ef þú ert að leita að því að samþætta FPGA tækni í efstu deildinni í vörur þínar eða kerfi, þá er snjall hreyfing að kaupa XCV200-6FG456C í lausu með okkur.Það uppfyllir iðnaðarstaðla og heldur þér á undan framtíðartækniþörfum.

XCV200-6FG456C eiginleikar

• Kerfishlið: XCV200-6FG456C býður upp á um það bil 236.666 kerfishlið.Þessi háa hliðatalning gerir kleift að útfæra flóknar samþættar stafrænar rökstýringar á einum flís og auka bæði afköst og fjölhæfni í ýmsum forritum.

• Rökfræðiauðlindir: Það felur í sér 1.176 stillanlegar rökfræðiblokkir (CLB) og 5.292 rökfræðifrumur.Þessi úrræði eru góð til að hanna sveigjanlegar og stigstærðar stafrænar hringrásir.Hægt er að forrita CLB til að framkvæma margs konar rökréttar aðgerðir en mikill fjöldi rökfræðifrumna gerir kleift að meðhöndla umfangsmikla rökfræðiaðgerðir og ferla.

• Minningu: Tækið veitir 57.344 bit af vinnsluminni, dreift meðal rökfræðiblokka þess.Þetta innbyggða vinnsluminni er notað fyrir forrit sem krefjast hraðrar og skilvirkrar gagnageymslu og sóknar, sem styður háhraða gagnaaðgerðir sem eru samþættir nútíma stafrænum kerfum.

• I/O getu: Með 284 inntak/úttakspinna auðveldar XCV200-6FG456C umfangsmikla tengibúnað.Þessir I/O pinnar styðja ýmsa merkisstaðla og gera FPGA kleift að eiga samskipti á áhrifaríkan hátt við aðra íhluti í kerfinu, svo sem minni tæki, örgjörvum og jaðartæki.

• Spenna og hitastig svið: Að starfa við nafnspennu 2,5V, með ásættanlegt svið frá 2.375V til 2.625V, er þessi FPGA hannað fyrir neyslu með litla kraft en viðheldur öflugri afköstum.Það getur starfað innan mótunarhitastigs á bilinu 0 ° C til 85 ° C og tryggt áreiðanleika við mismunandi umhverfisaðstæður.

Xcv200-6fg456c pinna aðgerðarmynd

The Xcv200-6fg456c pinna aðgerðarmynd er skipulögð framsetning á PIN -verkefnum FPGA, flokkuð í mismunandi banka (Banki 0 til banka 7).Hver bankahópar pinnar út frá virkni þeirra og líkamlegri staðsetningu á FPGA pakkanum.Númeragreining og merkingarkerfið fylgir ristamynstri þar sem línur eru táknaðar með bókstöfum (a, b, c osfrv.) Og dálkum með tölum (1, 2, 3, osfrv.), Sem auðveldar fljótt að bera kennsl á sérstaka pinna.Þessir bankar samsvara mismunandi inntak/framleiðsla aðgerðum, krafti, jörðu og sérstökum merkisleið.Pins er úthlutað ýmsum hagnýtum hópum, þar með talið almennum I/O (GPIO), oft merktir sem „G“ (almenn inntak/framleiðsla), „V“ (spennuframboð) og „O“ (framleiðsla).Kraftur og jarðpinnar eru merktir áberandi og tryggja stöðuga FPGA aðgerð.Sérstök tilgangspinna eins og aðföng klukka, endurstillingar og stjórnmerki eru auðkennd með táknum eins og „R“ eða „T.“Sumir pinnar þjóna einnig sérstökum samskiptahlutverkum, þar á meðal JTAG stillingum og háhraða klukku, fyrir forritun og kembiforrit.

XCV200-6FG456C blokkarmynd

Inntak/úttaksblokk

Skýringarmyndin táknar Inntak/úttaksblokk (IOB) Uppbygging XCV200-6FG456C FPGA, sem er aðili að Xilinx Virtex fjölskyldunni.Skýringarmyndin sýnir lykilatriði sem taka þátt í inntaks- og úttaksaðgerðum og varpa ljósi á gagnaflæði og stjórnkerfi.Í kjarna skýringarmyndarinnar eru þrír D flip-flops notaðir til að skrá merki fyrir inntak, framleiðsla og þrí-ríki stjórn.Útgangaskránni er stjórnað af OCE (Output Clock Enable) merkinu, sem ákvarðar hvenær framleiðsla gagna er fest.Að sama skapi er Tri-State skránni stjórnað af TCE (Tri-State Clock Virkja), sem gerir kleift eða slökkva á framleiðsla stuðpúða.Inntakaskráin tekur við komandi gögnum og beitir forritanlegri seinkun áður en það sendir það yfir í innri FPGA rökfræði í gegnum IBUF (inntak stuðpúði).Obuft (Tri-State Output Buffer) tryggir að FPGA geti annað hvort ekið merki á púðann (I/O pinna) eða sett það í háviðskiptaástand, allt eftir stjórnunarrökfræði.Veikur markvörður er með á púðanum til að viðhalda síðasta þekkta rökfræðinni þegar enginn virkur ökumaður er til staðar og kemur í veg fyrir óviljandi fljótandi aðstæður.Viðmiðunarspenna (VREF) er notuð fyrir ákveðna inntaksstaðla, svo sem SSTL eða HSTL, sem krefjast nákvæms spennustigs fyrir rétta notkun.Á heildina litið gerir þessi IOB uppbygging FPGA kleift að stjórna háhraða gagnaflutningi, styðja mismunandi I/O staðla og veita sveigjanlega stjórn á tímasetningu merkja og heiðarleika.

Serial stilling meistara/þræla

The Serial stilling meistara/þræla Blokk skýringarmynd sýnir stillingarferlið Virtex FPGA, sérstaklega XCV200-6FG456C, þegar það er forritað í Daisy-keðju stillingu með því að nota raðnúmer EEPROM (XC1701L).Í þessari uppsetningu starfar eitt Virtex tæki sem meistari, stjórnar stillingarklukkunni (CCLK) og sendir stillingargögn í röð til viðbótar þræla FPGA í keðjunni.Master FPGA hefur frumkvæði að stillingarferlinu með því að fullyrða forritamerkið og endurstilla öll tæki í keðjunni.Þegar frumstillingu er lokið bendir Init merkið til reiðu og stillingargögn streyma frá raðnúmeri EEPROM (XC1701L) yfir í DIN (gögn í) pinna Master FPGA.Master FPGA les gögn frá EEPROM og framsendir þau í gegnum Dout (gögn út) til síðari þræla FPGA, samstillt gagnaflutning með CCLK merkinu.Ljómandi merki er notað til að gefa til kynna árangursríka stillingu, með valfrjálsri uppspyrnu viðnám sem tryggir stöðugt hátt ástand þegar stillingum er lokið.XC1701L EEPROM er stjórnað af Master FPGA með því að nota CLK, Data, CE (Chip Enable) og endurstilla/OE (framleiðsla Virkja) merki, sem tryggir að geymd stillingargögn séu rétt sótt.Þessi stillingaraðferð er skilvirk til að forrita margar FPGA með því að nota eina EEPROM, draga úr utanaðkomandi raflögn flækjustig og tryggja að öll tæki fái samstillt stillingargögn.

XCV200-6FG456C forskriftir

|

Tegund |

Færibreytur |

|

Framleiðandi |

AMD Xilinx

|

|

Röð |

Virtex® |

|

Umbúðir |

Bakki |

|

Staða hluta |

Úrelt |

|

Fjöldi rannsóknarstofna/CLB |

1176 |

|

Fjöldi rökfræðiþátta/frumna |

5292 |

|

Heildar vinnsluminni |

57344 |

|

Fjöldi i/o |

284 |

|

Fjöldi hliðar |

236666 |

|

Spenna - framboð |

2.375V ~ 2.625V |

|

Festingartegund |

Yfirborðsfesting |

|

Rekstrarhiti |

0 ° C ~ 85 ° C (TJ) |

|

Pakki / mál |

456-BBGA |

|

Pakki birgjabúnaðar |

456-fbga (23x23) |

|

Grunnvörunúmer |

Xcv200 |

XCV200-6FG456C forrit

Fjarskipti og tengslanet

XCV200-6FG456C skar sig fram úr í fjarskiptum og netforritum vegna getu þess til að takast á við háhraða gagnaútgáfur og flókin verkefnavinnsluverkefni.Hátt hliðatalning og öflug I/O getu þess gerir það kleift að styðja aðgerðir eins og pakkavinnslu, merkis mótun/demodulation og villuleiðréttingar samskiptareglur.

Stafræn merkisvinnsla (DSP)

Tilvalið fyrir DSP forrit, þessi FPGA getur framkvæmt skjótar og flóknar stærðfræðilegar útreikningar sem krafist er í hljóð- og myndbandsvinnslutækni.Hvort sem það er fyrir margmiðlunarkerfi, raddþekkingu eða streymisþjónustu, öflug vinnslu getu XCV200-6FG456C og innbyggð minni styður skilvirka og hágæða merki vinnslu.

Iðnaðareftirlitskerfi

Í sjálfvirkni iðnaðarins veitir XCV200-6FG456C nauðsynlegan árangur til að stjórna stjórnkerfi og sjálfvirkni netum.Geta þess til að framkvæma mörg stjórnunarverkefni samtímis en tryggja að viðbragðstími gerir það að verkum að það hentar fyrir forrit í vinnslustýringu, vélfærafræði og sjónræn sjón.

Lækningatæki

Nákvæmni og hraði FPGA er frábær í læknisfræðilegum myndgreiningum og greiningarbúnaði, þar sem hann hjálpar til við vinnslu flókinna reiknirita fyrir myndgreiningar eins og Hafrannsóknastofnun, ómskoðun og CT skannanir.Geta XCV200-6FG456C tryggir að það geti séð um mikla afköst gagna og flókna vinnslu sem krafist er í nútíma lækningatækni.

XCV200-6FG456C Svipaðir hlutar

XCV200-6FG456C forritunarskref

Forritunarskref fyrir XCV200-6FG456C:

1. Hönnunarfærsla

Upphafsstig FPGA forritunar felur í sér að skilgreina stafræna rökfræði og virkni kerfisins.Þetta er hægt að gera með því að nota vélbúnaðarlýsingu tungumál (HDL) eins og VHDL eða Verilog, þar sem þú skrifar kóða sem tilgreinir hvernig FPGA vinnur gögn og hefur samskipti við annan vélbúnað.Hægt er að nota skýringartæki sem eru fáanleg í FPGA hönnunarhugbúnaði eins og Xilinx ISE eða Vivado.Þessi aðferð felur í sér að búa til sjónræn framsetning á rökfræði með því að draga og sleppa íhlutum, sem sumum finnst leiðandi en að skrifa kóða.

2. Synthesis

Þegar hönnuninni er lokið er næsta skref nýmyndun, þar sem tæki eins og XILinx's XST (Xilinx Synthesis Technology) umbreytir HDL kóða þínum eða skýringarmynd í netlista.Þessi netlisti lýsir hringrásinni hvað varðar almenna stafræna hluti, svo sem rökfræðihlið og skrár.Nýmyndunarferlið felur einnig í sér að hámarka hönnunina til að uppfylla kröfur um afköst og lágmarka auðlindanotkun fyrir skilvirka FPGA rekstur.

3. Framkvæmd

Framkvæmdarferlið byrjar með þýðingu og sameinar hönnun þína með þvingunarskrám sem tilgreina breytur eins og klukkutíðni og PIN -verkefni.Eftir þýðingu úthlutar kortlagningin þáttum netlistans þíns til sérstakra líkamlegra auðlinda á FPGA, eins og uppflettitöflum (LUT) og flip-flops.Staðsetningin og leiðarstigið ákvarðar síðan líkamlega staðsetningu hvers íhluta innan arkitektúr FPGA og setur tengslin á milli með forritanlegum samtengdum auðlindum.Þessi áfangi er frábært til að ná fram afköstum mælikvarða, þar með talið klukkutíðni.

4. Bitstream kynslóð

Eftir árangursríka staðsetningu og leið, býr tólið til bitastraums, tvöfaldur stillingarskrá sem inniheldur allar forritunarupplýsingar fyrir FPGA.Oft er mælt með því að líkja eftir endanlegri hönnun eftir stöðvun til að tryggja að bitastraumurinn muni hegða sér eins og búist var við við aðstæður.Þetta sannprófunarskref hjálpar til við að forðast hugsanleg mál við raunverulegan rekstur.

5. Stillingar

Lokaskrefið felur í sér að hlaða bitastrauminn í FPGA með því að nota ýmsar stillingaraðferðir.Þræla-röð stillingin, einfaldur og hagkvæmur valkostur, stillir FPGA um utanaðkomandi aðalbúnað sem sendir gögn í röð.Í meistarasvæðum les FPGA sjálfstætt bitastrauminn frá meðfylgjandi raðps.Fyrir háhraða stillingar gerir SelectMap Mode kleift að utanaðkomandi örgjörvi muni hlaða gögn inn í FPGA fljótt.Að auki er JTAG stilling notuð ekki aðeins til forritunar heldur einnig til að prófa og kembiforrit, með því að nota venjulegt viðmót fyrir forritun í kerfinu og prófun á mörkum.

XCV200-6FG456C Kostir

Frammistaða

Xilinx Virtex serían, sem XCV200-6FG456C tilheyrir, er fínstillt fyrir háhraða afköst og býður upp á allt að 200 MHz.Þetta gerir það að verkum að það er vel hentað fyrir forrit sem krefjast skjótrar gagnavinnslu, að tryggja skilvirka meðhöndlun flókinna reiknirita og háhraðaaðgerða eins og fjarskipta, vinnslu og margmiðlunar.

I/O staðlar styðja

Þessi FPGA styður breitt úrval af inntak/framleiðsla staðla, þar á meðal LVTTL, LVCMOS, PCI, GTL, HSTL, SSTL, CTT og AGP.Slíkir umfangsmiklir I/O staðlar stuðlar að því að gera XCV200-6FG456C kleift að samþætta óaðfinnanlega við ýmsa kerfisíhluti og auka notagildi þess yfir fjölbreytt stafræn vistkerfi.Þessi sveigjanleiki gerir kleift að laga FPGA að mismunandi tengiaðstæðum án kerfisbreytinga.

Klukkustjórnun

XCV200-6FG456C felur í sér margar seinkunarlykkjur (DLLs) fyrir dreifingu og stjórnun klukku innan kerfisins.Þessar DLLs hjálpa til við að bæta tímasetningu og áreiðanleika kerfisins með því að veita nákvæm klukkutegund sem nauðsynleg eru fyrir samstilltar aðgerðir.Þessi eiginleiki er mikilvægur til að draga úr villum kerfisins og auka heildarárangur, sérstaklega í flóknum hönnun sem krefst nákvæmrar tímasetningar og samstillingar.

Hönnun sveigjanleika

Með 1.176 stillanlegum rökfræðiblokkum og 5.292 rökfræðifrumum býður XCV200-6FG456C verulegar rökfræðiauðlindir með getu til að innleiða fjölbreytt svið virkni.Allt frá einföldum lím rökfræði til flókinna stafrænna kerfa styður þetta FPGA flóknar hönnunarkröfur, sem gerir það tilvalið fyrir forrit í sérsniðnum tölvunarfræði, vinnslu stafrænna merkja og frumgerð.

Hröð frumgerð

FPGA eins og XCV200-6FG456C eru þekktir fyrir getu sína til að styðja við skjótar frumgerðir.Þetta tæki gerir ráð fyrir skjótum endurtekningum og hægt er að endurstilla það á vettvangi, sem er kostur fyrir þróunarlotur þar sem það dregur úr tíma til markaðarins.Það aðlagast einnig á skilvirkan hátt að því að breyta kröfum eða uppfærslum í forskriftum verkefnisins og tryggja að lokaafurðirnar séu uppfærðar með nýjustu tæknilegum stöðlum.

Sameiningargeta

Sameiningargeta XCV200-6FG456C auðveldar sameiningu margra stakra íhluta í einn flís.Þessi samþætting getur leitt til minni margbreytileika kerfisins, minni orkunotkunar og sparnaðar kostnaðar.Með því að lágmarka fjölda aðskildra íhluta sem þarf, einfaldar þessi FPGA hönnunarferli og bætir áreiðanleika og þjöppun heildarkerfisins.

XCV200-6FG456C umbúðir

XCV200-6FG456C er sviði forritanleg Gate Array (FPGA) úr AMD's Virtex® seríunni, hýst í 456 ball fínpitakúlukúlupakka (FBGA).

• Pakkategund: 456-fbga

• Pakkastærð: 23 mm x 23 mm

• Boltahöll: 1,0 mm

XCV200-6FG456C framleiðandi

XCV200-6FG456C er sviði forritanleg Gate Array (FPGA) sem upphaflega var þróað af Xilinx, fyrirtæki sem er þekkt fyrir afkastamikil forritanleg rökfræði tæki.Eftir kaup Xilinx eftir Amd, XCV200-6FG456C er nú tengt AMD sem núverandi framleiðanda.Hins vegar er þetta FPGA líkan úrelt og ekki lengur í framleiðslu.AMD heldur áfram að styðja við nýrri FPGA arkitektúr með aukinni afköstum, orkunýtni og lengri langlífi, sem gerir nútímalegan val ákjósanlegra fyrir nýja hönnun.

Niðurstaða

XCV200-6FG456C er fjölhæfur og háhraða FPGA, gagnlegur fyrir mörg tækniforrit.Þó að það sé ekki lengur gert er það samt góður kostur fyrir eldri kerfi sem þurfa áreiðanlega afköst.Þessi handbók hefur fjallað um hönnun sína, forritunarskref og hagnýta notkun, sem gerir það auðveldara að skilja hvernig hún virkar og hvernig það er hægt að nota.Eftir því sem nýrri FPGA verða tiltækir geturðu notað þessa þekkingu til að velja rétta FPGA fyrir þarfir þínar og bæta stafræna hönnun.

DataSheet PDF

Xcv200-6fg456c gagnablöð:

Um okkur

ALLELCO LIMITED

Lestu meira

Fljótur fyrirspurn

Vinsamlegast sendu fyrirspurn, við munum svara strax.

Algengar spurningar [FAQ]

1.. Hver er orkunotkun XCV200-6FG456C?

XCV200-6FG456C starfar við 2,5V, með spennusvið 2,375V til 2,625V.Raforkun er háð rökfræði nýtingu og klukkutíðni, en sem eldri FPGA getur það verið minna kraftmikið en nýrri Xilinx tæki.Íhuga ætti rétta orkustjórnun og hitaleiðni.

2. Hvernig er XCV200-6FG456C í samanburði við XCV200-6FG256C?

XCV200-6FG456C er með stærri pakka (456-bolta FBGA) samanborið við XCV200-6FG256C (256-Ball FBGA), sem býður upp á fleiri I/O pinna (284 á móti 172) og hugsanlega betri afköst fyrir forrit sem krefjast víðtækra tengi.Ef hönnun þín treystir á fleiri I/O getu er XCV200-6FG456C betra valið.

3. Get ég endurforritað XCV200-6FG456C margoft?

Já, XCV200-6FG456C er SRAM-undirstaða FPGA, sem þýðir að hægt er að endurforrita það ótakmarkaðan fjölda sinnum svo framarlega sem krafturinn er til staðar.Hins vegar þarftu utanaðkomandi óstöðugt minni (EEPROM eða Flash) til að halda bítstraumnum eftir rafmagnsferil.

4.. Styður XCV200-6FG456C háhraða raðsamskipti?

XCV200-6FG456C styður marga I/O staðla eins og LVTTL, LVCMOS, PCI, GTL, HSTL og SSTL, en það er ekki með innbyggða háhraða serdes (raðnúmer/deserializer) eða sendingar eins og nútíma FPGAs.Fyrir forrit sem krefjast háhraða raðtengla (t.d. PCIE, Gigabit Ethernet, eða HDMI) skaltu íhuga nýrri FPGA gerðir.

5. Hvernig ber XCV200-6FG456C saman við nýrri FPGA gerðir?

XCV200-6FG456C tilheyrir eldri kynslóð FPGA.Í samanburði við nútíma Virtex FPGA hefur það lægri hliðafjölda, hægari klukkuhraða og takmarkaða orkunýtni.Nýrri gerðir bjóða upp á meiri rökfræðiþéttleika, meira innbyggt minni, háþróaða DSP -blokkir og minni orkunotkun, sem gerir þau betri fyrir nútíma forrit.

AD73322Ar pinout, eiginleikar og tæknilegar upplýsingar útskýrðar

á 2025/03/21

EP20K100EFC324-1X FPGA: Aðgerðir, forskriftir, forrit og forritunarleiðbeiningar

á 2025/03/20

Vinsæl innlegg

-

Flóknar tölvuuppsetningar tölvur: hvernig þær breyttu tölvunarfræði?

á 8000/04/18 147778

-

USB-C pinout og eiginleikar

á 2000/04/18 112030

-

Notkun Xilinx Unified Simulation Primitives: Alhliða leiðbeiningar um FPGA hönnun og uppgerð

á 1600/04/18 111351

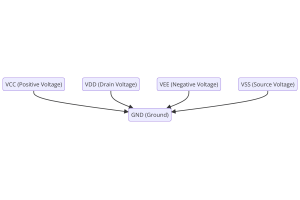

-

Aflgjafaspenna í rafeindatækni: Merking VCC, VDD, VEE, VSS og GND

á 0400/04/18 83786

-

RJ45 tengihandbók: Pinout, raflögn, snúrutegundir og notar

á 1970/01/1 79584

-

Endanleg leiðarvísir um vír litakóða í nútíma rafkerfum

Hvernig rafkerfin okkar nota liti er ekki bara fyrir útlit.Hver vírlitur gefur nú til kynna ákveðna aðgerð, sem gerir það auðveldara að bera kennsl á og meðhöndla rafmagn íhluta rétt við uppsetning...á 1970/01/1 66973

-

Hreinsunarhandbók: Virkni, einkenni, prófanir og skipti fyrir ákjósanlegan afköst vélarinnar

Hreinsunarventillinn er lykilatriði í kerfi bíls sem hjálpar til við að halda loftinu hreinu með því að stjórna eldsneytisgufum áður en þeir geta sloppið út í andrúmsloftið.Þetta hjálpar ekki aðein...á 1970/01/1 63108

-

Gæði (q) þáttur: jöfnur og forrit

Gæðaþátturinn, eða 'Q', er mikilvægur þegar athugað er hversu vel inductors og resonators vinna í rafrænu kerfum sem nota útvarpsbylgjur (RF).'Q' mælir hversu vel hringrás lágmarkar orkutap og hefu...á 1970/01/1 63043

-

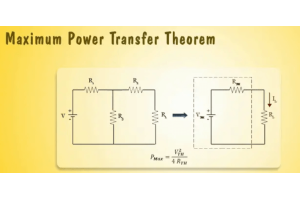

Að ná hámarksafköstum með hámarks valdaflutnings setningu

Setning hámarks aflflutnings útskýrir hvernig orka frá uppruna, svo sem rafhlöðu eða rafall, rennur til tengds álags.Það sýnir nákvæmlega ástand þar sem álagið fær mestan kraft.Þessi grein fjallar ...á 1970/01/1 54097

-

A23 rafhlöðuforskriftir og eindrægni

A23 rafhlaðan er lítil, strokkalaga rafhlaða með háspennu.Einnig kallað 23A, 23AE eða MN21, það keyrir á 12 volt og miklu hærri en AA eða AAA rafhlöður.Sérstök hönnun þess gerir það fullko...á 1970/01/1 52195